针对有线电视和通讯应用的PIN二极管衰减器的结构

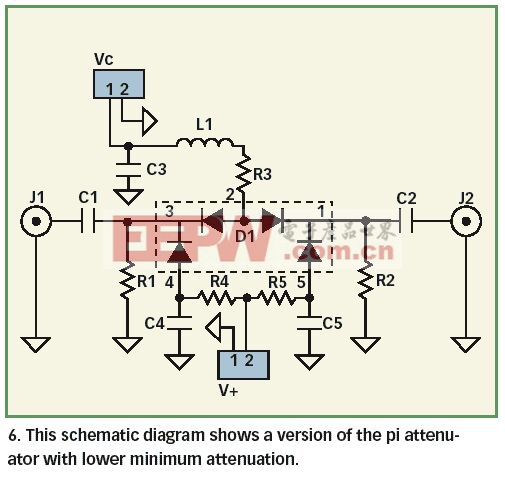

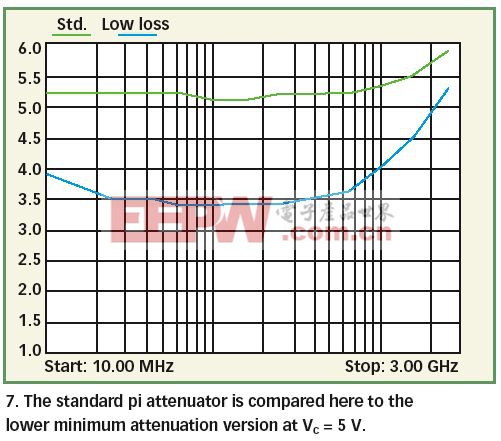

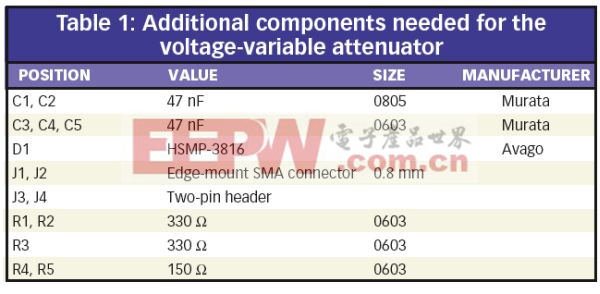

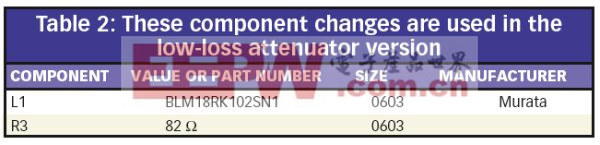

增加通过串联二极管的电流可以降低衰减下限。将控制电压保持在最大值5V,减小电阻R3的阻值就可以增大偏移电压,这可以通过给阻断RF的电阻R3(表2)串联一个表面贴装铁酸盐珠状电感而实现。在整个频率范围内,与传统的瓷芯多层片状电感相比,这种铁酸盐珠状电感具有更高的阻抗。图6给出了低衰减下限衰减电路的示意图,图7中给出了在Vc=5V的条件下与标准衰减电路的比较结果。

为了建立π衰减器的性能模型以便于进一步分析,安捷伦公司的高级设计系统(ADS)计算机辅助工程(CAE)软件为工程师们提供了模拟四元二极管π衰减器性能的技术支持范例。相应文件可以从www.edasupportweb.soco.agilent.com.的Agilent Eesof知识中心的“Examples”部分下载。

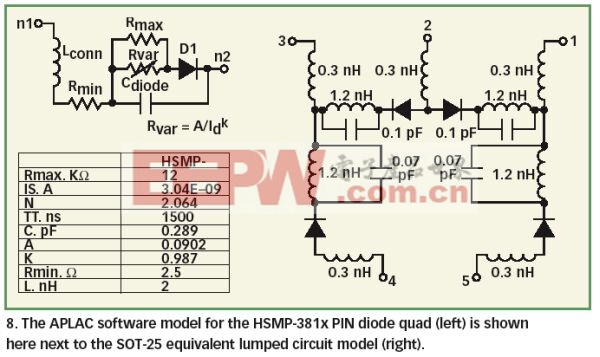

另外,包含在高频建模工具APLAC CAE软件包(www.aplac.com)中的PIN二极管模型也可以预测在给定正向偏移的条件下RF阻值。图8的左边给出了HSMP-3816 PIN二极管的APLAC模型,将APLAC模型与SOT-25等效电路模型(图8右边)结合在一起,就可以使设计人员在模拟过程中研究分析封装的寄生效应。

衰减器相关文章:衰减器原理

评论