高速USB OTG--便携设备绝佳的互连解决方案

B设备将先后执行数据线脉冲调制和VBUS脉冲调制,分别通过使能数据线上拉电阻(全速和高速设备为D+,低速设备为D-)5~10ms和驱动VBUS实现。VBUS必须要有足够长的时间对其电容充电,这个时间应能保证不大于13μF的电容充电至2.1V(OTG设备的电容是6.5μF或更小),从而不会对标准主机的96μF或更大的电容充电至2.0V。该限制保证了从B设备引来的VBUS电流不会破坏标准主机的端口。

A设备检测到数据线脉冲调制或者VBUS脉冲调制后,首先复位总线,然后发送Set_feature命令而先不进行设备的枚举,此时B设备尚处在默认的从端状态。如果Set_feature命令成功执行,说明B设备为两用OTG设备,A设备(使用HNP协议)挂起VBUS准备让B设备交换为主机方式接管总线。如果Set_feature命令执行失败,说明B设备为外设式OTG设备,于是A设备使能VBUS准备开始一个传输事务(此时,A设备只是被唤醒,并未改变工作方式)。当A设备认为总线上没有传输需要时,挂起VBUS以结束该事务。这种A设备自动检测B设备是否支持HNP的特征称为“No Silent Failure”。

USB得以成功的其中一项秘诀在于完善的认证测试程序。这道程序能检测设备是否符合规范且能否与其他USB设备共同运作,唯有通过认证测试的设备才能贴上USB的认可标签。目前,认证测试有两种途径,可通过USB Compliance Workshop(Plugfests)或个别的测试实验室进行测试。以上两种方式都能将通过检测的设备列入符合规范USB设备的整合厂商名单中。

USB OTG 评估板测试

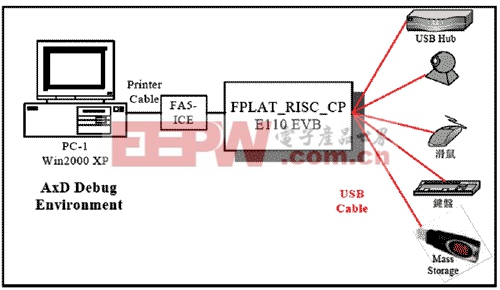

1 USB EHCI 主端控制器测试

每个设备应该能响应USB规范所定义的控制请求。主端应该能利用主端控制器经USB缆线送出控制需求到USB设备。

|

图3 EHCI 主端控制器测试架构 |

|

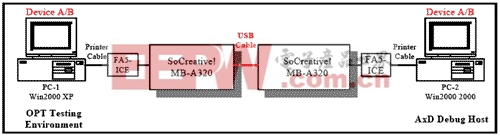

图4 互测SNP和HNP的连接架构 |

利用两台USB OTG开发板互测SNP和HNP的连接架构如图4所示。

|

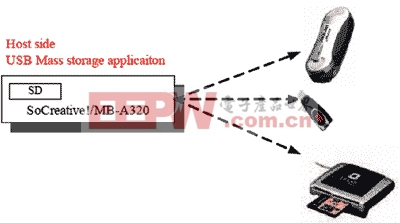

图5 大量存储的应用测试 |

如图5所示,设计一个SD卡主端应用来做演示, SD卡的大量存储用以测试FOTG200功能。FOTG200是智原的USB 2.0 OTG控制器, 能作为一个双重角色。作为主设备,它包含一个USB主端制器,能支援所有速度的事务。无须软件干涉的情形下,主端制器能处理一个基于事务的数据结构以减去主控CPU的负担,自动地在USB总线上转送和接收数据。作为从设备,每个端点,除了端点0,都承担可编程的HS/FS传输类型提供弹性以适应各式各样的应用。

在这个应用上, USB子系统由USB IP核、EHCI HCD控制器、USB大量存储Class驱动、文件系统和SD卡设备驱动所组成。因此,主端设备能够读/写文档到SD卡(外部设备)。顺便也能验证大量存储Class驱动和Bulk IN/OUT传输的功能。

评论