以太网控制器ENC28J60及其接口技术

2.4 时钟输出引脚

CLKOUT引脚可为系统中的其他设备提供时钟源。上电后CLKOUT引脚保持低电平,复位结束后OST计数。OST期满后,CLKOUT输出频率为6.25 MHz的时钟。

时钟输出功能通过ECOCON寄存器禁止、调整和使能。时钟输出可设置为1、2、3、4、8分频,上电后默认为4分频。ECOCON寄存器配置改变以后,CLKOUT引脚有80~320 ns的延迟(保持低电平),然后按照设定输出固定频率的时钟信号。

软件或者RESET引脚上的复位信号不会影响ECOCON寄存器的状态。PowerDown模式也不会影响时钟的输出。当禁止时钟输出时,CLKOUT引脚保持低电平。

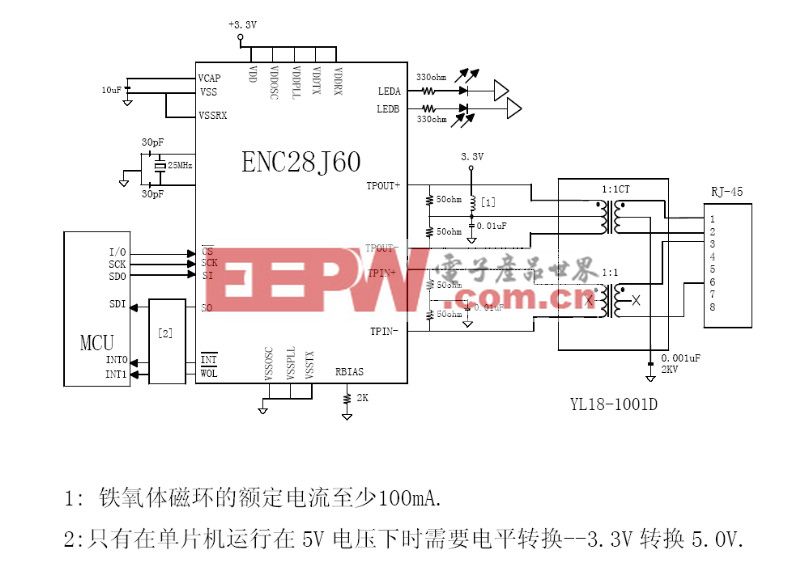

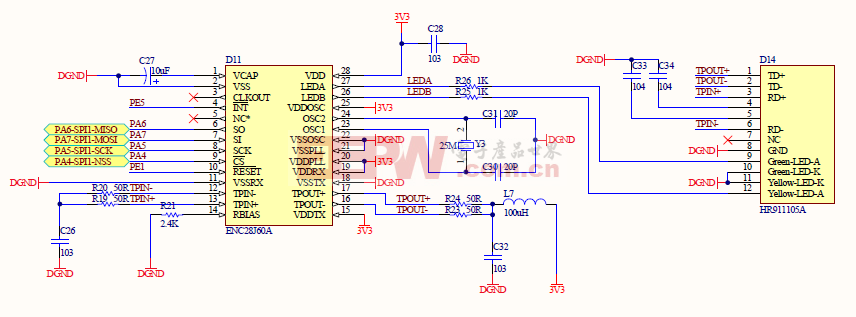

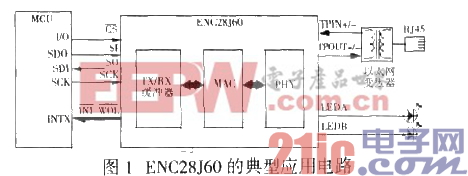

2.5 变压器、终端和其他外部器件

为了实现以太网接口ENC28J60,需要几个标准的外部器件: 脉冲变压器、偏置电阻、储能电容和去耦电容。

差分输入引脚(TPIN+/TPIN-),需要一个1∶1变比的脉冲变压器来实现10BASET。差分输出引脚(TPOUT+/TPOUT-),需要一个变比为1∶1、带中心抽头的脉冲变压器。变压器需要有2 kV或更高的隔离能力,防静电。对变压器的详细要求请参考芯片手册第16章“电气特性”。每个部分都需要通过2个50 Ω、精度为1%的电阻和1个0.01 μF的电容串联后接地。

笔者采用的是中山汉仁公司的集成以太网隔离变压器RJ45插座HR901170A。

ENC28J60内部的模拟电路需要在RBIAS引脚和地之间跨接1个2 kΩ、1%的偏置电阻。部分数字电路工作在2.5 V,以降低功耗;ENC28J60内部集成1个2.5 V的调节器来产生所需的电压,需在VCAP引脚和地之间接1个10 μF的电容保证供电的稳定性(该2.5 V调节器不是为外部负载设计的)。

所有的供电引脚(VDD、VDDOSC、VDDPLL、VDDRX、VDDTX)必须接在外部的同一个3.3 V电源上;同理,所有的地(VSS、VSSOSC、VSSPLL、VSSTX)必须接在同一个外部地上。每个供电引脚和地之间应当接1个0.1 μF的陶瓷电容去耦(电容要尽可能接近供电引脚)。

驱动双绞线接口需要较大的电流,所以电源线应尽可能宽,与引脚的连接尽可能短,以降低电源线内阻的消耗。

2.6 输入输出电平

ENC28J60是一个3.3 V的CMOS器件,但它设计得非常容易统一到5 V系统中去:SPI、CS、 SCK、SI输入和RESET引脚一样,都可承受5 V电压。当SPI和中断输入与3.3 V驱动的CMOS输出不兼容时,可能需要一个单向的电平转换器。74HCT08 (四与门), 74ACT125(四三态缓冲器)和许多具有TTL电平输入的5 V CMOS缓冲器芯片都可以提供所需的电平转换。

2.7 LED配置

LEDA和LEDB引脚在复位时支持极性自动检测。既可直接驱动LED,又可灌电流驱动。复位时ENC28J60检测LED的连接,并按照PHLCON寄存器的默认设置来驱动。运行过程中的LED极性转换直到下一次系统复位后才能被检测到。LEDB的连接比较特殊,在复位过程中检测它的连接,决定如何初始化PHCON1寄存器的PDPXMD位。如果LEDB直接驱动LED,则PHCON1.PDPXMD位被清零,PHY工作在半双工模式;如果LEDB吸收反向电流点亮LED,则PHCON1.PDPXMD被置位,PHY工作在全双工模式;如果LEDB没有连接,则PHCON1.PDPXMD复位后的值不确定。这时主控制器必须适当设置该位,以使PHY工作在所需的状态(半双工或全双工)。

3 软件接口

3.1 SPI接口

SPI接口( Serial Peripheral Interface )是一种同步、全双工串行接口,基于主从配置,是一个4线接口——主出/从入(MOSI),主入/从出(MISO),串行时钟(SCK),从机选择(SSEL)。

在同一总线上可以有多个主机或者从机,但同一时刻只能有一个主机和一个从机能够进行通信。在一次数据传输过程中,数据是同步进行发送和接收的:主机向从机发送1字节数据,从机也向主机返1字节数据。数据传输原则上是全双工的;但实际上,大多数情况下只有一个方向上的数据流包含有意义的数据。

SPI格式的主要特性是SCK信号的无效状态和相位,数据传输的时钟由主机提供。常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于从机输出数据位的时钟相位。CPOL和CPHA的设置决定了数据取样的时钟沿。

取决于CPOL和CPHA的设置不同,SPI共有4种模式,如表1所列。

评论