基于PCI软“核”的PCI总线接口设计与实现

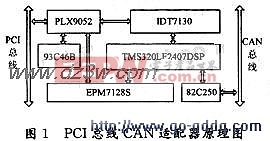

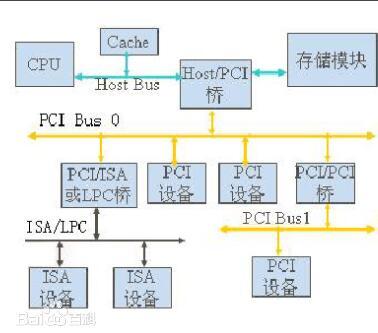

PCI总线是通过主桥电路挂接在Host CPU上的局部总线,典型的PCI局部总线系统结构如图1所示。PCI的外部设备既可以作为PCI总线目标设备(Slave),实现基本的传送要求,也可以作为PCI总线的主控设备(Master),访问其他PCI总线设备及系统的其他资源。用户在实际应用中可以根据实际需求来设计设备的功能。

由于PCI总线规范[1]定义了严格的电气特性和时序要求,因而开发基于PCI总线的接口卡有一定的难度。它要求在接口卡和终端设备之间有一个总线接口控制器,以解码PCI总线线范并完成数据传送,这需要开发人员对PCI总线规范有深刻的理解并具有较高的计算机开水平。开发PCI接口大体有两种方式:使用专用的PCI接口芯片和可编程器件。如果使用ASIC厂家提供的专用接口芯片,用户使用到的只是部分PCI接口功能,会造成了一定的资源浪费,而且芯片价格高,不经济。使用可编程器件设计,将厂家提供的PCI软“核”引入可编程器件中,根据插卡的功能进行最优化,不必实现所有的PCI功能机以将PCI插卡的用户逻辑与PCI接口逻辑集成在一个芯片上,实现紧凑的系统设计。当系统升级时,只需更改可编程器件的逻辑,无需更新PCB版图。许多可编程器件产生厂商都提供经过测试的PCI接口功能模块,如Xilinx公司的LogiCore,Altera公司的AMPP(Altera Megafunction Partners Prongam)。下面介绍用Xilinx公司的LogiCore来实现控制连接在PCI局部总线上的外设。

1 Xilinx公司的LogiCore简介

Xilinx公司的LogiCore逻辑框图如图2所示。可以看出,该LogiCore的功能是将左边复杂的PCI接口转换成右边的用户接口信号:周期控制信号(包括用于配置PCI接口的信号CEG[255:0])、从设备控制信号、主设备控制信号、状态机信号等。其主要的功能是起一个桥梁作用,完成用户设备与PCI总线的信息传送,并且可以在Bus Master方式下直接访问系统主存储器。图2的LogiCorem逻辑框图只给出Xilinx的LogiCore中与PCI Master控制器有关的关键信号。现在就以上信号进行介绍:

PCI Host 端总线接口:

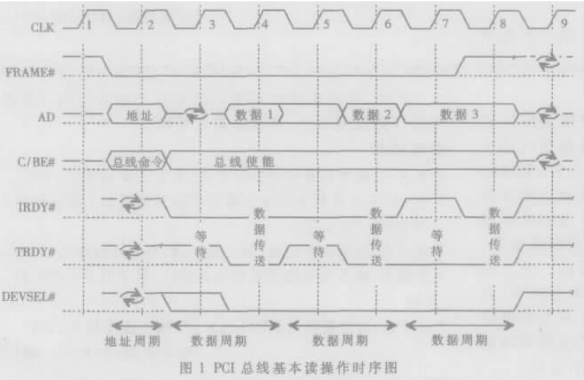

AD[31:0] 时分复用地址/数据信号,在帧信号有效的一个时钟AD[31:0]上的信号为地址信号。

C/BE[3:0] 命令/字节使能信号,在帧信号有效的第一个节拍,指示总线作业类型。

FRAMF 由总线上设备驱动,指明传输的起始时间和终止时间,在该信号有效期间表示总线传输开始,当该信号无效时,传输的是最后一个数据节拍。

IRDY 由总线主设备驱动,读操作时表示总线传输开始,当该信号无效时,传输的最后一个数据节拍。

IRDY 由总线主设备驱动,读操作时表示已准备好接受数据,写操作时表示有效数据已经在数据上。

TRDY 由从设备驱动,读操作时从设备正在把有效数据放在数据总线上;写操作时表示从设备准备接受来自Host的数据。

DEBSEL 译码出的地址在该设备的地址范围内时,则该信号有效。

IDSEL 配置读、写期间由Host发出的片选信号。

STOP 从设备向Host表示停止目前信号的传送。

PAR 奇偶校验信号,它通过AD[31:0]和C/BE[3:0]进行奇偶校验。

PERR 该信号只报告数据奇偶校验错。

SERR 该信号只报靠地址奇偶校验错,或者特殊命令序列中的数据奇偶校验错。

INTR_A 表示PCI设备请求中断。

REQ 表示总线主设备向仲裁器发出要占用PCI总线的请求。

User端总线接口:

ADIO[31:0] 地址数据复用总线,该总线由三态缓冲器驱动。

ADDR[31:0] 在地址周期,输出PCI总线当前作业的起始地址。

DEVSEL_USR 是DEVSEL信号的“克隆”版本。

相关推荐

-

-

zqh1630 | 2013-03-11

-

-

-

-

-

xiaotaoqi637 | 2013-12-24

-

四弦 | 2012-04-21

-

-

hbu2009 | 2014-03-24

-

-

-

落月风情 | 2013-08-15

评论