基于PLD和串行总线扩展系统控制功能

在进行复杂系统的架构开发时,架构师和设计师很少对设计的系统控制方面予以重视。最好的情况是,系统控制在整个系统的设计考虑中排第二位。而最坏的情况是直接被遗忘,直到设计后期,板上只有很小的空间能实现系统控制功能,也不可能再有时间来重新进行架构设计。

过去,设计师常常会使用一些方法来解决这些问题:请软件设计师想办法在软件中实现某些控制功能;在电路板上四处增加小的PLD,因为受到电路板空间限制而不得不忍受布局布线的不便和拥挤;或者,以时间进度为由,牺牲某些功能。这些方法听起来都不怎么样。我们需要一种方法,最大限度地减少电路板的面积和布线,同时减少微处理器的使用并且实现所需的功能。

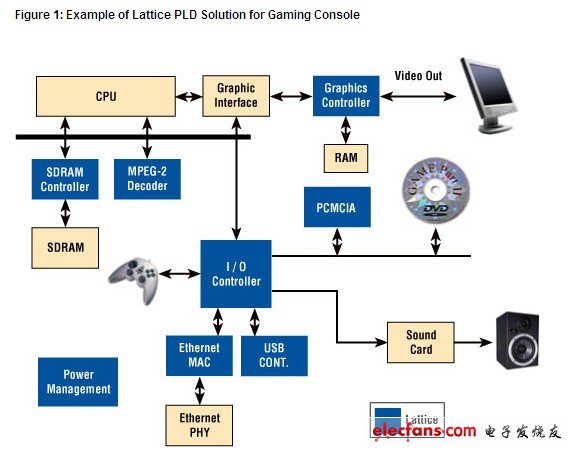

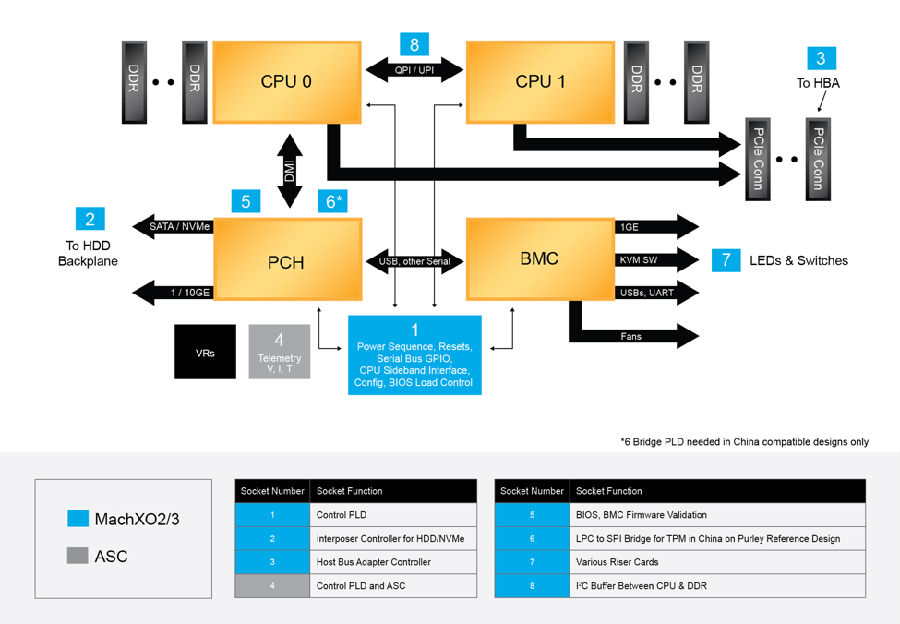

CPLD和小型FPGA往往是这种情况下的首选解决方案。使用CPLD和FPGA,设计人员可以不再需要集中监测和控制,而更多的采用本地化控制和分配。创建一条通信路径,尽可能地减少中央处理器和分布的PLD之间的连接,将会是一个最接近理想的解决方案。幸运的是,串行外设接口(SPI)标准和内部集成电路(I2C)标准就是理想的低开销的通信路径,他们最初分别由Motorola公司和Phillips公司开发。这两个标准并非设计用于提供大多数数据路径所需的高吞吐量,但它们在监控和控制应用中表现良好,相比之下这些应用中的延迟问题不是那么重要。

将FPGA和CPLD的灵活性和这些低开销总线相结合,为系统设计师提供了大量的系统控制功能,同时最大限度地减少所需的电路板面积。

低速串行总线

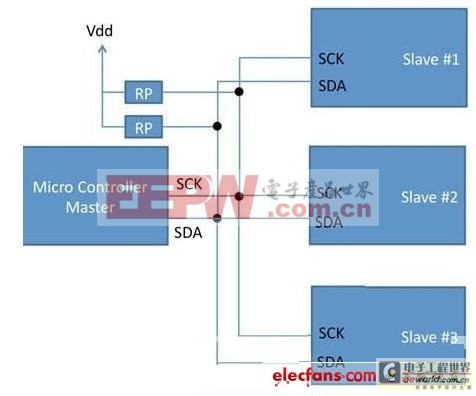

从物理学和电气学的角度来看,SPI和I2C都是低开销的总线标准,一般从电路板实现的角度来看就很容易理解。I2C只需要两个信号来实现:SDA(数据线)和SCK(时钟线)。这些线路都是漏极开路,并要求端接上拉电阻。这些连线可以跨越多个主器件和从器件,如图1所示。该电路还需要的唯一一个额外要求就是使用适当的端接上拉电阻来处理线路电容。两线总线上的多个主器件的问题需要使用总线仲裁来处理消息冲突。但是使用一个简单的专用总线结构和一个主器件,这些问题就可以全部解决。

图1 典型的I2C连接

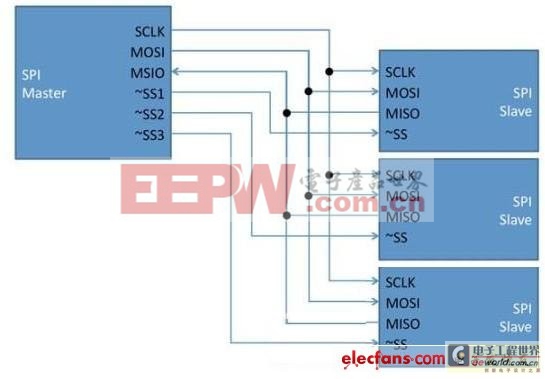

SPI是一个4线串行总线,由于总线上仅允许有一个主器件因而无需总线仲裁。此外,还有两个数据引脚,都不是真正的双向引脚。MOSI(主器件输出,从器件输入)线负责将数据发送给外设;MISO(主器件输入,从器件输出)负责将数据发送给主器件。时钟(SCLK)和从器件选择(SS)信号提供总线控制,它们都是由主器件驱动。虽然这种安排避免了总线仲裁的需要,但是需要使用更多的信号。

图2 典型的三个从器件的SPI总线

今天使用哪种串行总线方面的限制相对较少。截至2006年,NXP(原Phillips)不再需要许可证即可使用I2C协议。应当指出的是,获取I2C从器件地址仍需收取费用。然而,对于外设无需与外界通信的应用,这是没有必要的。而SPI是一个没有正式规范文档而被广泛使用的标准。然而,该标准已经在许多不同的嵌入式处理器中实现,由此看出虽然它没有正式规范文档,但是并未阻碍其广泛使用。

低开销的I2C和SPI两种标准被广泛采用并且集成到微控制器和外设中。

系统监测和控制

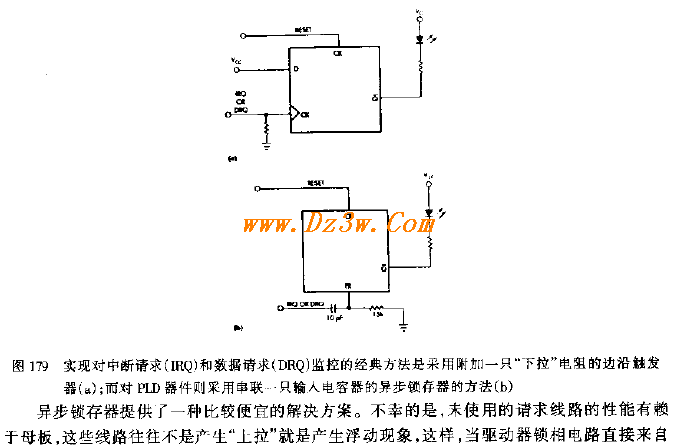

单块电路板上的应用监测和控制相对比较简单。复位、中断线路和选择线路可以直接由微控制器或本地PLD控制。然而,在多块电路板的系统中则需要进行集中控制,因而尽量减少连接的数量是很重要的。这可以通过使用低开销的串行总线与PLD进行通信来实现,如图3中所示。

评论