FPGA实现CAN总线通信节点设计

在项目的特殊环境要求下, CAN总线通信要求使用FPGA作为系统中的主控制器, 较之传统设计使用的单片机, FPGA能够在速度和体积上有更好的适应性。FPGA 一方面减少了电路板的复杂程度, 缩短了实现周期; 另一方面, 其丰富的资源、超高的性能和灵活的可编程性, 提高了整个设备的可靠性, 大大增强了电路板设计的灵活性和可扩展性。文中通过设计FPGA 的接口电路, 并利用Verilog语言来编程实现CAN节点之间的通信功能。

1 CAN 接口硬件设计

1.1 CAN 节点的系统构成

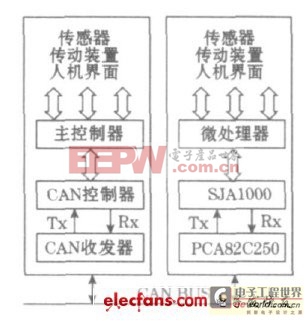

一般来说, 每个CAN 模块能够被分成3 个不同的功能块,其结构如图1所示。CAN总线收发器提供CAN协议控制器与物理总线之间的接口, 控制从CAN 控制器到总线物理层或相反的逻辑电平信号。它的性能决定了总线接口、总线终端、总线长度和节点数, 是影响整个总线网络通信性能的关键因素之一。CAN 控制器执行在CAN 规范里规定的完整的CAN 协议, 它通常用于报文缓冲和验收滤波, 对外具有与主控制器和总线收发器的接口。主控制器负责执行应用的功能, 例如控制命令的发送、读传感器和处理人机接口等。它通过对CAN 控制器进行编程, 来控制CAN 总线的工作方式和工作状态, 以及进行数据的发送和接收。

图1 CAN 模块系统构成

1.2 接口电路设计

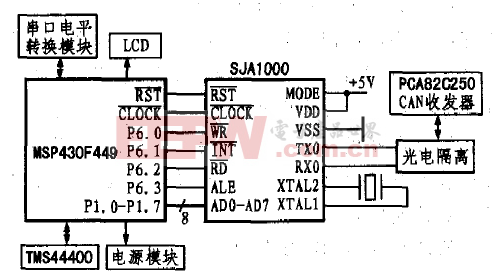

接口电路如图2所示。SJA1000的AD0~ AD7地址数据复用端口、ALE地址锁存端口、RD、WR、片选CS端口均通过转换芯片与FPGA的I /O口相连。SJA1000 的中断输出信号INT连入FPGA, 使CAN通信可以采用中断或查询方式。RST 端口的电路实现SJA1000的上电自动复位功能。MODE 模式选择端接+ 5 V, 设置SJA1000控制器为Intel模式。SJA1000 的时钟晶振采用16MH z, 频率调整电容取15 pF. R16为终端电阻,设计中取120Ω。 CAN 驱动器PCA82C250 的RS脚为工作模式选择位, 接地工作于高速模式, 接高工作于待机模式。系统通过电阻R14将芯片设定于斜率控制模式, 电阻值为47 kΩ , 这时CAN 总线应工作于低速模式, 可提高CAN 总线抵抗射频干扰的能力。在这种情况下, 可直接使用非屏蔽双绞线作为总线。

设计中有2点需要特别注意: 第一点是FPGA 并没有与SJA1000直接相连。这是因为对于设计选取的FPGAXCV600, 其接口电平不支持5 V TTL的I/O 标准, 如果与5 VI/O标准的SJA1000直接相连, 将可能导致FPGA 管脚电流过大, 造成器件锁死或者烧毁。为此采用双向总线收发器74ALVC164245, 把SJA1000的5 V TTL电平信号AD0 ~ AD7、

fpga相关文章:fpga是什么

通信相关文章:通信原理

晶振相关文章:晶振原理 双绞线传输器相关文章:双绞线传输器原理

评论