浅谈CPLD在IGBT驱动设计中的应用

随着国民经济的不断发展,变频调速装置的应用越来越广泛。如何打破国外产品的垄断,已成为一个严肃的课题摆在我国工程技术人员的面前。

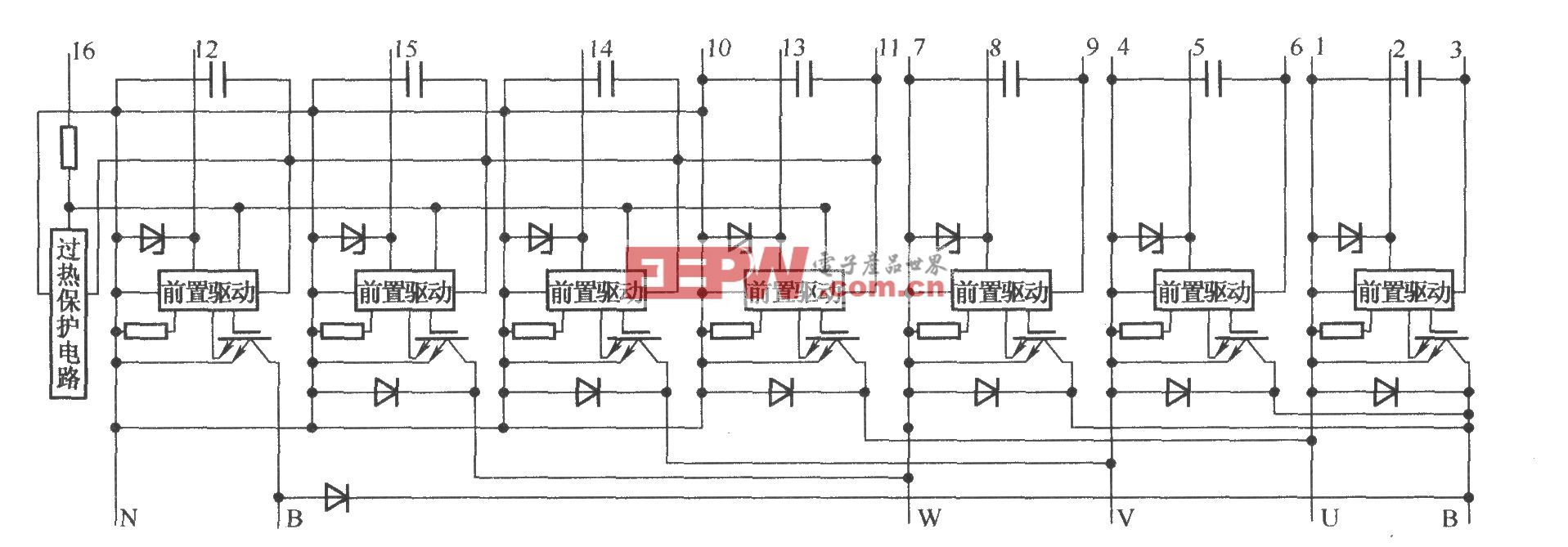

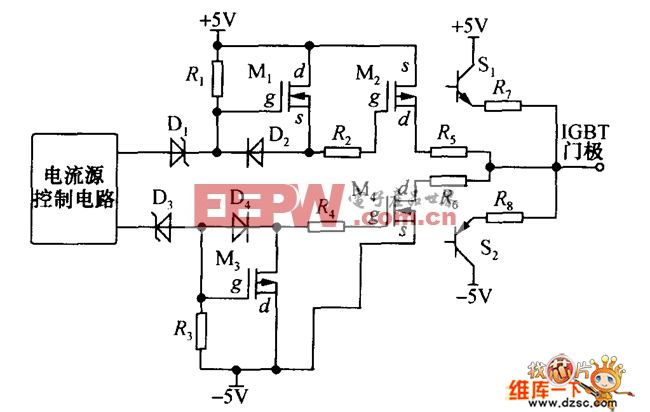

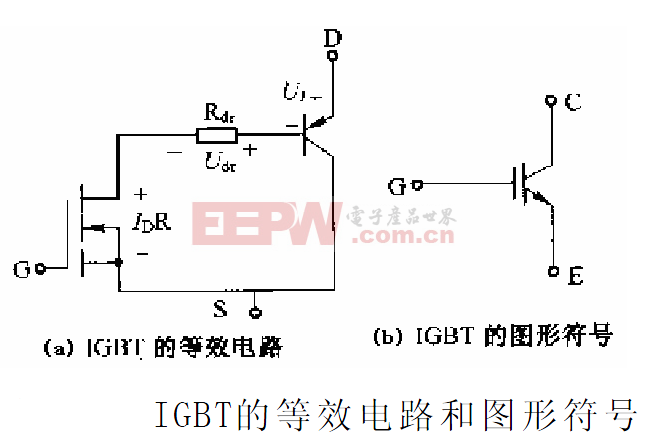

本文引用地址:http://www.amcfsurvey.com/article/236508.htm在某型号大功率变频调速装置中,由于装置的尺寸较大,考虑到结构和散热的条件,主控板上DSP产生的PWM信号需经过较长的距离才能送到IGBT逆变单元中。为保证PWM信号传输的准确性和可靠性,必须解决以下几个问题:首先是抗干扰问题,变频器工作时,IGBT的开关动作会产生高频干扰信号;其次是如何保证PWM信号的前、后沿质量,减少IGBT开关动作的过渡过程;最后是如何减少布线电感,尽可能缩短PWM信号传输距离,避免过多的内部连线。

1 总体设计

原则上说,从触发电路到IGBT栅极和发射极的引线应做到既短又一致。但随着变频调速装置功率的不断增大,装置的尺寸也在增大,散热条件要求更高。由于结构设计上的种种原因,真正做到这点有很多实际困难。

DSP产生的PWM信号既可以采用串行方式又能以并行方式进行传输,但这两种方式都有着各自的特点。采用并行方式传输信号(即每一个IGBT模块的栅控端都接一根信号线)会造成系统内部接线过多、接地困难,抗干扰性大大降低,这种情况尤以采用了多重化、多电平技术的变频装置为甚。若利用串行方式,PWM信号的传输速率又受到介质的极大限制。在目前诸多传输介质中,只有光纤具有损耗低、频带宽、重量轻、不受电磁干扰等突出优点。GI型光纤用LED做光源时,传输速率可达140Mbit/s,传输损耗可忽略不计。IGBT的工作频率通常很少用在15kHz以上,因此以异步串行方式高速传输PWM信号时,采用光纤作为传输介质是唯一的选择。

在串行的PWM信号送到IGBT的栅控端之前,还需将该信号转化为并行形式。尽管采用普通的串/并转换芯片可以实现上述功能,但这些芯片的最高工作频率有限,如74166的最高工作频率为35MHz,对于目前广泛采用多重化和多电平技术的变频装置来讲,这种工作频率显然有着较大的局限性。尤其是在实时性、快速性要求甚高的电机控制领域,不可能采用应答方式完成信号的传输,因此接收端需要有较强的纠错和容错能力。若采用普通的芯片,难以只用一两片芯片完成上述功能。但CPLD具有极强的灵活性,内含128个宏单元,最高工作频率可达167MHz(以Cypress CY37128为例),可以只用一两片芯片就能完成较复杂的逻辑功能,因此CPLD与光纤的结合是解决大功率变频器中信号传输的最好选择。系统信号流程图如图1所示。

2 通讯方案

异步串行格式的一个数据帧包括1位起始位和8位数据位,最后是停止位。起始位规定为0,8位数据位由高到低顺次发送,前7位组成1个编码字符,第八位为奇偶校验位。停止位可以选择1位、1位、2位。从系统实际要求出发,我们对标准的异步串行格式进行了修改,将三相PWM信号进行编码,用以下数据格式发送到信号转换单元:0-a3c3a2c2a1c1-V-1111。其中0为起始位,a1、a2、a3分别对应三相逆变桥每个桥臂的栅控信号,c1、c2、c3分别对应三相逆变桥每个桥臂的封锁信号,V是一位校验位,最后四个1为结束标志位。信号转换单元的CPLD接收到该信号后,将此串行PWM信号转换为并行形式。另一方面,为保证逆变单元能够正常工作,还需将逆变单元故障信号送到上位机以供故障诊断。

故障信号以以下串行编码格式送出:0-a1a2a3a4a5a6-V-1111,0为起始位,a1、a2、a3分别对应每个桥臂的驱动故障信号,a4为过热信号,a5、a6为通讯故障 信号,V为校验位,最后四个1为结束标志位。上位机板上的CPLD将此信号转换为并行形式。事实上,PWM信号和故障信号的处理过程是相同的。

对于异步串行通讯,通常要保证发送的信号在接收端能被正确接收,往往采用两类同步处理办法:一类是使用硬件手段实现通信协议的部分功能;另一类是使用各种短小的帧来实现通信功能。在本系统,由于实时控制对时间的要求,不可能采用上述形式的通讯方案。因此根据系统实际需要,数据传输采用起止式同步方案,即用 “0”代表起信号,“1”代表止信号。在不发送信息时,一直发送止信号。第一个由“1”到“0”的转换表示字符的开始收端检测到这个转换后控制位时钟输出,以便对接受信号进行码位中点取样判决。

针对系统的实际要求,为确保数据通讯的正确性,在正常工作以前,DSP模块必须向信号转换单元固定发送一个标志字。只有当信号转换单元连续几次正确收到标志字后,才能建立正常通讯。在正常通讯时,为避免随机干扰的作用,只有在连续出现多次帧错误的情况下,信号转换单元才向上位机发出通讯故障信号,以确保系统工作的稳定性。

3 CPLD的实现

20世纪90年代,引起数字系统设计方式发生突破性变革的技术是VHDL设计技术。VHDL Very High Speed Integrated Circuit VHSIC Hardware Description Language作为IEEE-1076标准所规范的硬件描述语言,非常适用于可编程逻辑器件的应用设计,并正在得以普及。采用自顶向下的设计方法,是用VHDL设计系统硬件最突出优点之一。

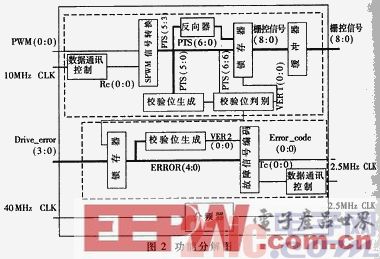

通过前面对数据流和通讯方案的分析,按照自顶向下的原则,我们对信号处理单元进行功能分解,将其分解到下面的各个单元中,见图2。通过功能分解,我们可以看到,单元内部构造可以分为三个部分:一部分对栅控信号进行处理;另一部分对故障信号进行处理;最后一部分用于产生控制故障信号发送的时钟。

从图2我们可以发现栅控信号处理部分与故障信号处理部分都含有功能相同单元:校验位生成单元、数据通信控制单元及锁存单元,因此可以对以上这些单元进行参数化设计。在参数化设计以前,我们还需要构造一些公共的基本元件,如触发器、寄存器、计数器和同步器等。这以后,我们就可以对前面提到的功能相同的单元进行参数化设计。

在进行参数化设计以前,我们需要对各功能单元的输入输出信号进行分析以确定信号使用的数据类型。由于IGBT控制问题的特殊性,在这里我们统一使用Bit和Bit-vector型数据。Bit型数据只有两种状态:“0”和“1”,可以有效地防止多态数值系统给控制和编程带来的麻烦。

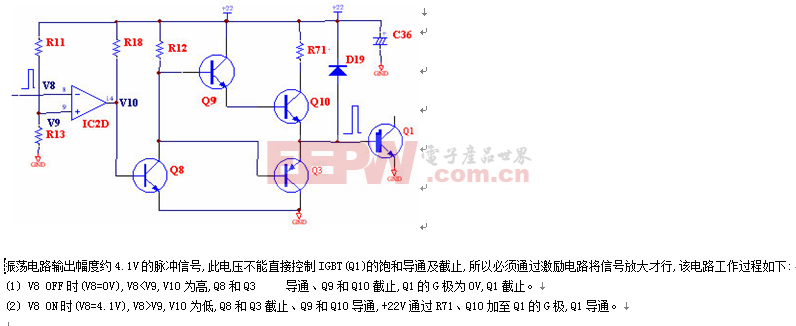

在进行传统的电子线路设计时,设计师的工作是按电路原理图将各个单元电路和器件连接起来,形成一个完整的系统。而在利用VHDL设计电路时,设计师所要完成的不过就是将那些用VHDL语言描述的单元电路和器件连接起来。在这个意义上,利用VHDL语言进行设计与利用传统方法设计没有太大的区别,但采用自顶向下的设计方法时,VHDL具有无可比拟的优越性。作为一种硬件描述语言 VHDL语言有别于一般的计算机语言。它既有并行执行的语句,又有只能顺序执行的语句。利用VHDL这种特性,我们可以将整个系统分成若干个相对比较独立的模块来进行电路设计。在下面的程序中,进程COUNTER描述了一个16位计数器,它通过对40MHz时钟进行分频,产生进程CONTROLLER所需的2.5MHz时钟。进程CONTROLLER构造了一个发送控制计数器,它通过对进程COUNTER所产生的时钟信号进行计数,产生故障信号的发送控制信号。

评论