一种基于PLL的P波段可控频率源

频率源作为电子系统的核心,是决定电子系统性能的关键设备。雷达、通信、电子侦察和对抗设备中,高性能的频率源是实现其整体设备高性能指标的关键技术之一。频率源的相位噪声和杂散抑制的性能直接影响整个系统的性能。其中采用锁相环设计的频率源具有输出频率高、频率稳定度高、频率纯、低相噪、杂散抑制好等优点。

本文引用地址:http://www.amcfsurvey.com/article/235733.htm锁相环的基本原理

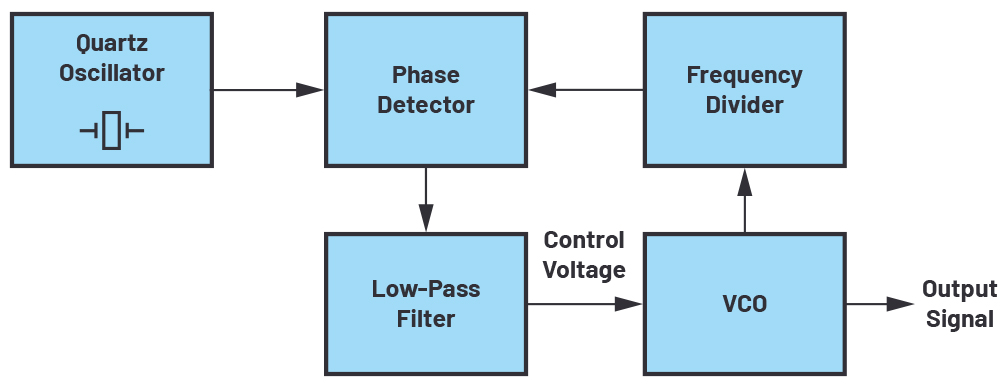

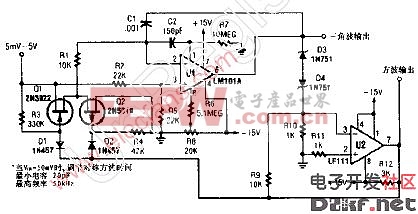

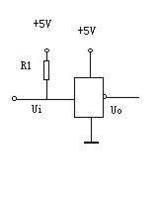

PLL(锁相环)是一种反馈控制电路,PLL在工作的过程中,当输出信号的频率与输入信号的频率相同时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是PLL名称的由来。PLL通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,鉴相器把输入信号的相位与压控振荡器输出信号的相位进行比较,输出一个正比于两个输入信号相位差的电压(或者电流)加到环路滤波器上,抑制噪声和高频分量后,再加到压控振荡器上,控制其频率变化,使输入信号与压控振荡器信号之间的相位差逐渐减小,最后达到动态锁定。锁相环的基本结构如图1。

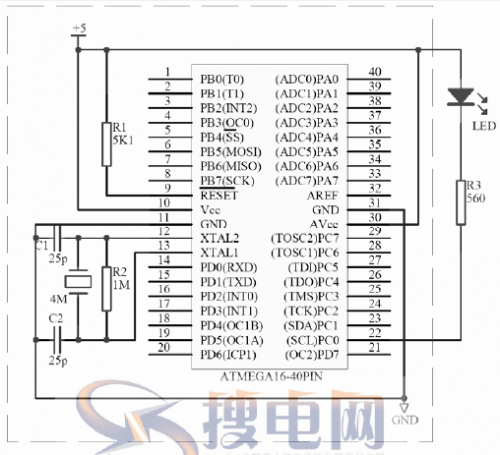

其中N分频器是由单片机编程控制的,因此这种合成器又体现了程序设计和锁相技术的结合。从总体结构看,它由单片机、锁相环和可编程分频器三部分组成。

评论