数字钟设计与制作

引言

本文引用地址:http://www.amcfsurvey.com/article/235666.htm本文采用CMOS数字集成电路实现了一种数字钟电路,该电路设计包括了时序逻辑电路、组合逻辑电路、数码管显示电路和脉冲信号产生电路等内容,内容涉及面宽、综合性强,是电子技术自主性实验教学的典型案例。

系统设计方案

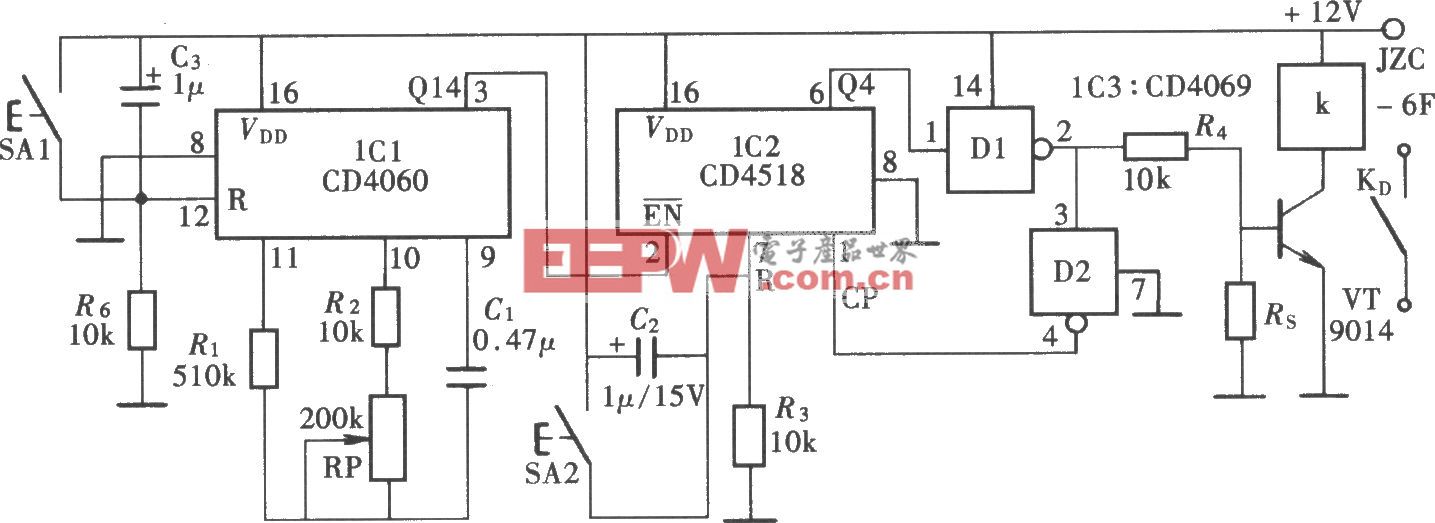

数字时钟是一个对标准频率(1Hz)进行计数的计数电路。在计数时,如果起始时间和当前时间不一致,还需要加一个校时电路。本次设计以数字电路为主,实现对时、分、秒的计时装置,周期为24小时,显示满刻度为23时59分59秒,并具有校时功能的数字电子钟。本次设计的数字钟电路主要采用中规模CMOS集成电路,以电池作电源,通过共阴极LED数码管显示时钟。电路由秒脉冲产生模块、计数器模块、译码显示模块和校时电路模块组成。系统组成框图如图1所示。

尘埃粒子计数器相关文章:尘埃粒子计数器原理 脉冲点火器相关文章:脉冲点火器原理

评论