秘籍!嵌入式系统电源设计决巧,搞定电压转换!

高效能的嵌入式系统电源电路设计一般比较复杂,设计人员在设计独特的多重电压级时需满足精准的电压、电流、纹波、噪声滤波、同步化、软启动和电源分隔等要求。本文根据硬件设计大侠在一些嵌入式系统电源电路设计技巧,整理出嵌入式系统电源设计秘籍,9大电压转换诀窍!奉献给EEPW网友们,在嵌入式电源电路的设计中好好把握,也让大家节省设计所需的宝贵时间。

本文引用地址:http://www.amcfsurvey.com/article/234443.htm1.高瞻远瞩,需细思量:FPGA系统,DSP系统,包括现在风头正劲的ARM为主的32位微处理器嵌入式系统都是多电源低电压供电。此外,对于采用电池供电的便携式嵌入式系统的电源来说,还要有电源管理的考虑。

嵌入式系统电源设计的好坏直接决定了系统设计的成败。出现电源设计问题的原因一方面是由于设计者硬件设计经验不足;另一方面是集成稳压芯片品种繁多、手册说明不规范,特别是有些厂商LDO, 以及DC-DC转换器的说明使用,让人似懂非懂。

2.知己知彼,掌握秘籍:

嵌入式系统电源一般有这么几种类型的电源引脚:用于向内核供电,一般为3.3V,1.8 V;分别给PLL、振荡器、复位电路,包括ADC部分供电,一般为3.3V,2.5V,2.0V,1.8 V,1.5V,1.2V等;分别用于给外设I/O口线、USB收发器以及外部总线接口I/O口线供电,一般为3.3 V,2.5V,1.8V等。系统的键盘、显示电路的供电电压需要+5 V电源。通过对整个控制系统的控制要求和性能进行分析,一般系统的负载电流大约为3 A以上,一般的系统需要使用至少3组以上的电源供电。

随着尺寸的减小,晶体管击穿电压变得更低,最终,当击穿电压低于电源电压时,就要求减小电源电压。因此,随着速度的提高和复杂程度的上升,对于高密度器件而言,不可避免的后果就是电源电压将从 5V 降至 3.3V,甚至1.8V,1.2V等。

因此,作为系统电源设计人员,面临着连接 5V 和 3.3V ,1.8V等电压转换的的任务。这个任务不仅包括逻辑电平转换,同时还包括为3.3V 系统供电、转换模拟信号使之跨越 1.2V/1.8V/3.3V/5V 的障碍。

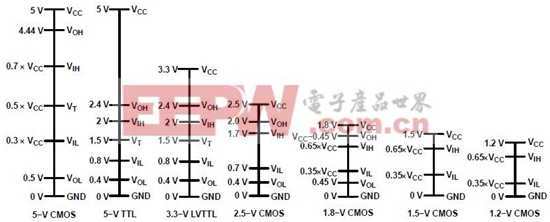

秘籍:看懂下面的图1,神马多嵌入式电源电压转换就是浮云!

图1:不同电压电平转换的阀值

图1显示了不同电源电压和器件技术的阈值电平。为了成功连接两个器件,必须符合以下要求:

①. 驱动器的VOH 必须高于接收器的VIH。

②. 驱动器的VOL 必须低于接收器的VIL。

③. 驱动器的输出电压不得超过接收器的I/O 电压容差。

3.九大诀窍,分而治之:

①5V 至 3.3V 转换完全可以用LDO稳压器解决

如果电路负载电流不大对效率无要求的设计,可以使用简单稳定的线性稳压器。如果电流需求较高的话,可能就需要开关稳压器解决方案。对成本敏感的应用,也可能需要简单的分立式二极管稳压器。

图2:几种电源性能比较

标准三端线性稳压器的压差通常是 2.0-3.0V。要把 5V 可靠地转换为 3.3V,压差为几百个毫伏的低压降 (Low Dropout, LDO)稳压器,是此类应用的理想选择。LDO 内部由四个主要部分组成:1. 导通晶体管2. 带隙参考源3. 运算放大器4. 反馈电阻分压器。

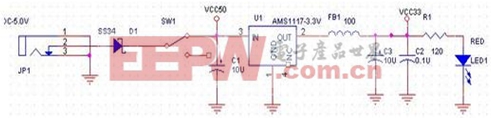

诀窍:在选择 LDO 时,重要的是要知道如何区分各种LDO。器件的静态电流、封装大小和型号是重要的器件参数。根据具体应用来确定各种参数,将会得到最优的设计。如下图采用LM1117-3.3V(AMS1117)供电

图3:低压差LDO的5V到3.3V的典型运用

稳压二极管相关文章:稳压二极管的作用

评论