在SMPS应用中选择IGBT和MOSFET的比较

公式1 获得所需导通di/dt的栅极驱动阻抗

把平均GFS值运用到公式1中,得到栅极驱动电压Vdrive=10V,所需的 di/dt=600A/μs,FCP11N60典型值VGS(avg)=6V,Ciss=1200pF;于是可以计算出导通栅极驱动阻抗为37Ω。由于在图3的曲线中瞬态GFS值是一条斜线,会在Eon期间出现变化,意味着di/dt也会变化。呈指数衰减的栅极驱动电流Vdrive和下降的Ciss作为 VGS的函数也进入了该公式,表现具有令人惊讶的线性电流上升的总体效应。

同样的,IGBT也可以进行类似的栅极驱动导通阻抗计算,VGE(avg) 和 GFS可以通过IGBT的转换特性曲线来确定,并应用VGE(avg)下的CIES值代替Ciss。计算所得的IGBT导通栅极驱动阻抗为100Ω,该值比前面的37Ω高,表明IGBT GFS较高,而CIES较低。这里的关键之处在于,为了从MOSFET转换到IGBT,必须对栅极驱动电路进行调节。

传导损耗需谨慎

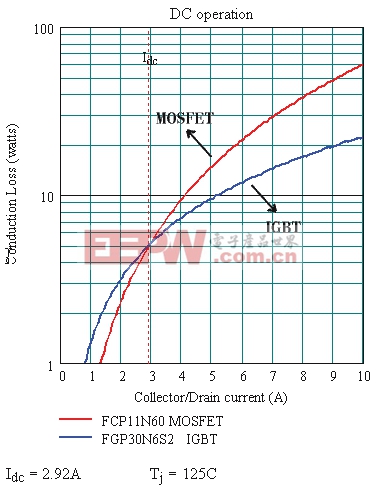

在比较额定值为600V的器件时,IGBT的传导损耗一般比相同芯片大小的600 V MOSFET少。这种比较应该是在集电极和漏极电流密度可明显感测,并在指明最差情况下的工作结温下进行的。例如,FGP20N6S2 SMPS2 IGBT 和 FCP11N60 SuperFET均具有1℃/W的RθJC值。图4显示了在125℃的结温下传导损耗与直流电流的关系,图中曲线表明在直流电流大于2.92A后, MOSFET的传导损耗更大。

图4 传导损耗直流工作

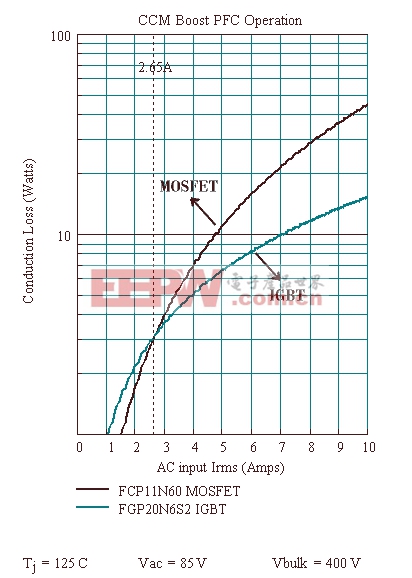

图5 CCM升压PFC电路中的传导损耗

不过,图4中的直流传导损耗比较不适用于大部分应用。同时,图5中显示了传导损耗在CCM (连续电流模式)、升压PFC电路,125℃的结温以及85V的交流输入电压Vac和400 Vdc直流输出电压的工作模式下的比较曲线。图中,MOSFET-IGBT的曲线相交点为2.65A RMS。对PFC电路而言,当交流输入电流大于2.65A RMS时,MOSFET具有较大的传导损耗。2.65A PFC交流输入电流等于MOSFET中由公式2计算所得的2.29A RMS。MOSFET传导损耗、I2R,利用公式2定义的电流和MOSFET 125℃的RDS(on)可以计算得出。把RDS(on)随漏极电流变化的因素考虑在内,该传导损耗还可以进一步精确化,这种关系如图6所示。

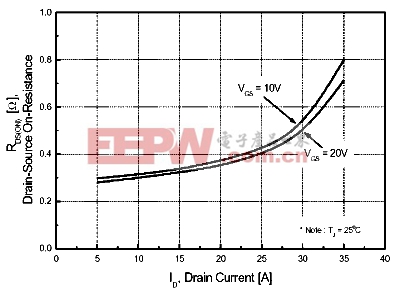

图6 FCP11N60(MOSFET): RDS(on)随IDRAIN和VGE的变化

一篇名为“如何将功率MOSFET的RDS(on)对漏极电流瞬态值的依赖性包含到高频三相PWM逆变器的传导损耗计算中”的IEEE文章描述了如何确定漏极电流对传导损耗的影响。作为ID之函数,RDS(on)变化对大多数SMPS拓扑的影响很小。例如,在PFC电路中,当FCP11N60 MOSFET的峰值电流ID为11A——两倍于5.5A (规格书中RDS(on) 的测试条件) 时,RDS(on)的有效值和传导损耗会增加5%。

在MOSFET传导极小占空比的高脉冲电流拓扑结构中,应该考虑图6所示的特性。如果FCP11N60 MOSFET工作在一个电路中,其漏极电流为占空比7.5%的20A脉冲 (即5.5A RMS),则有效的RDS(on)将比5.5A(规格书中的测试电流)时的0.32欧姆大25%。

![]()

公式2 CCM PFC电路中的RMS电流

式2中,Iacrms是PFC电路RMS输入电流;Vac是 PFC 电路RMS输入电压;Vout是直流输出电压。

在实际应用中,计算IGBT在类似PFC电路中的传导损耗将更加复杂,因为每个开关周期都在不同的IC上进行。IGBT的VCE(sat)不能由一个阻抗表示,比较简单直接的方法是将其表示为阻抗RFCE串联一个固定VFCE电压,VCE(ICE)=ICE×RFCE+VFCE。于是,传导损耗便可以计算为平均集电极电流与VFCE的乘积,加上RMS集电极电流的平方,再乘以阻抗RFCE。

图5中的示例仅考虑了CCM PFC电路的传导损耗,即假定设计目标在维持最差情况下的传导损耗小于15W。以FCP11N60 MOSFET为例,该电路被限制在5.8A,而FGP20N6S2 IGBT可以在9.8A的交流输入电流下工作。它可以传导超过MOSFET 70% 的功率。

虽然IGBT的传导损耗较小,但大多数600V IGBT都是PT (Punch Through,穿透) 型器件。PT器件具有NTC (负温度系数)特性,不能并联分流。或许,这些器件可以通过匹配器件VCE(sat)、VGE(TH) (栅射阈值电压) 及机械封装以有限的成效进行并联,以使得IGBT芯片们的温度可以保持一致的变化。相反地,MOSFET具有PTC (正温度系数),可以提供良好的电流分流。

关断损耗 —问题尚未结束

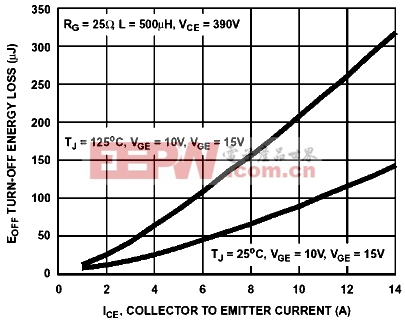

在硬开关、钳位感性电路中,MOSFET的关断损耗比IGBT低得多,原因在于IGBT 的拖尾电流,这与清除图1中PNP BJT的少数载流子有关。图7显示了集电极电流ICE和结温Tj的函数Eoff,其曲线在大多数IGBT数据表中都有提供。这些曲线基于钳位感性电路且测试电压相同,并包含拖尾电流能量损耗。

图7 本图表显示IGBT的Eoff随ICE及Tj的变化

图2显示了用于测量IGBT Eoff的典型测试电路, 它的测试电压,即图2中的VDD,因不同制造商及个别器件的BVCES而异。在比较器件时应考虑这测试条件中的VDD,因为在较低的VDD钳位电压下进行测试和工作将导致Eoff能耗降低。

降低栅极驱动关断阻抗对减小IGBT Eoff损耗影响极微。如图1所示,当等效的多数载流子MOSFET关断时,在IGBT少数载流子BJT中仍存在存储时间延迟td(off)I。不过,降低Eoff驱动阻抗将会减少米勒电容 (Miller capacitance) CRES和关断VCE的 dv/dt造成的电流注到栅极驱动回路中的风险,避免使器件重新偏置为传导状态,从而导致多个产生Eoff的开关动作。

ZVS和ZCS拓扑在降低MOSFET 和 IGBT的关断损耗方面很有优势。不过ZVS的工作优点在IGBT中没有那么大,因为当集电极电压上升到允许多余存储电荷进行耗散的电势值时,会引发拖尾冲击电流Eoff。ZCS拓扑可以提升最大的IGBT Eoff性能。正确的栅极驱动顺序可使IGBT栅极信号在第二个集电极电流过零点以前不被清除,从而显著降低IGBT ZCS Eoff 。

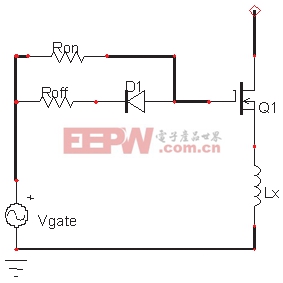

MOSFET的 Eoff能耗是其米勒电容Crss、栅极驱动速度、栅极驱动关断源阻抗及源极功率电路路径中寄生电感的函数。该电路寄生电感Lx (如图8所示) 产生一个电势,通过限制电流速度下降而增加关断损耗。在关断时,电流下降速度di/dt由Lx和VGS(th)决定。如果Lx=5nH,VGS(th)= 4V,则最大电流下降速度为VGS(th)/Lx=800A/μs。

图8 典型硬开关应用中的栅极驱动电路

总结

在选用功率开关器件时,并没有万全的解决方案,电路拓扑、工作频率、环境温度和物理尺寸,所有这些约束都会在做出最佳选择时起着作用。在具有最小 Eon损耗的ZVS 和 ZCS应用中,MOSFET由于具有较快的开关速度和较少的关断损耗,因此能够在较高频率下工作。对硬开关应用而言,MOSFET寄生二极管的恢复特性可能是个缺点。相反,由于IGBT组合封装内的二极管与特定应用匹配,极佳的软恢复二极管可与更高速的SMPS器件相配合。

评论