高效能低电压Power MOSFET及其参数与应用

前言

近年来,产业的发展、有限的资源及日益严重的地球暖化现象,促使环保节能的观念逐渐受到重视,更造就各项新能源的开发,能源利用技术及新式组件或装置的发展,而能源政策的推广更使得能源概念的商机逐渐扩大。

为了满足节能和降低系统功率损耗的需求,需要更高的能源转换效率,这些与时俱进的设计规范要求,对于电源转换器设计者会是日益严厉的挑战。为应对此需求,除使用各种新的转换器拓扑(topology)与电源转换技术来提高电源转换效率之外,新式功率组件在高效能转换器中所扮演的重要角色,亦不容忽视。其中,Power MOSFET目前已广泛应用于各种电源转换器。本文将简述Power MOSFET的特性、参数与应用,除针对目前低电压Power MOSFET的发展趋势做简单介绍外,还将简单比较新一代低压Power MOSFET的性能。

Power MOSFET的参数与应用

电源设计工程师在选用Power MOSFET设计电源时,大多直接以Power MOSFET的最大耐压、最大导通电流能力及导通电阻等三项参数做出初步决定。但实际上,在不同的应用电路中,Power MOSFET的选用有更细腻的考虑因素,以下将简单介绍 Power MOSFET的参数在应用上更值得注意的几项重点。

1 功率损耗及安全工作区域(Safe Operating Area, SOA)

对Power MOSFET而言,决定其最大功率损耗是由温度及接触-包装外壳间之热阻所决定,即:

(1)

(1)

由上式可知,若能够有效减少热阻,则Power MOSFET所能承受之的最大功率损耗就可以获得提升。因此,工艺的最大改进目标就是减少热阻。

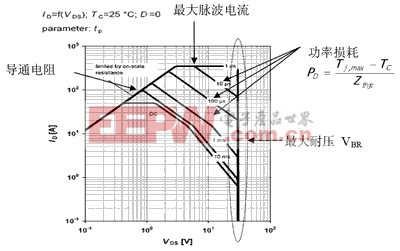

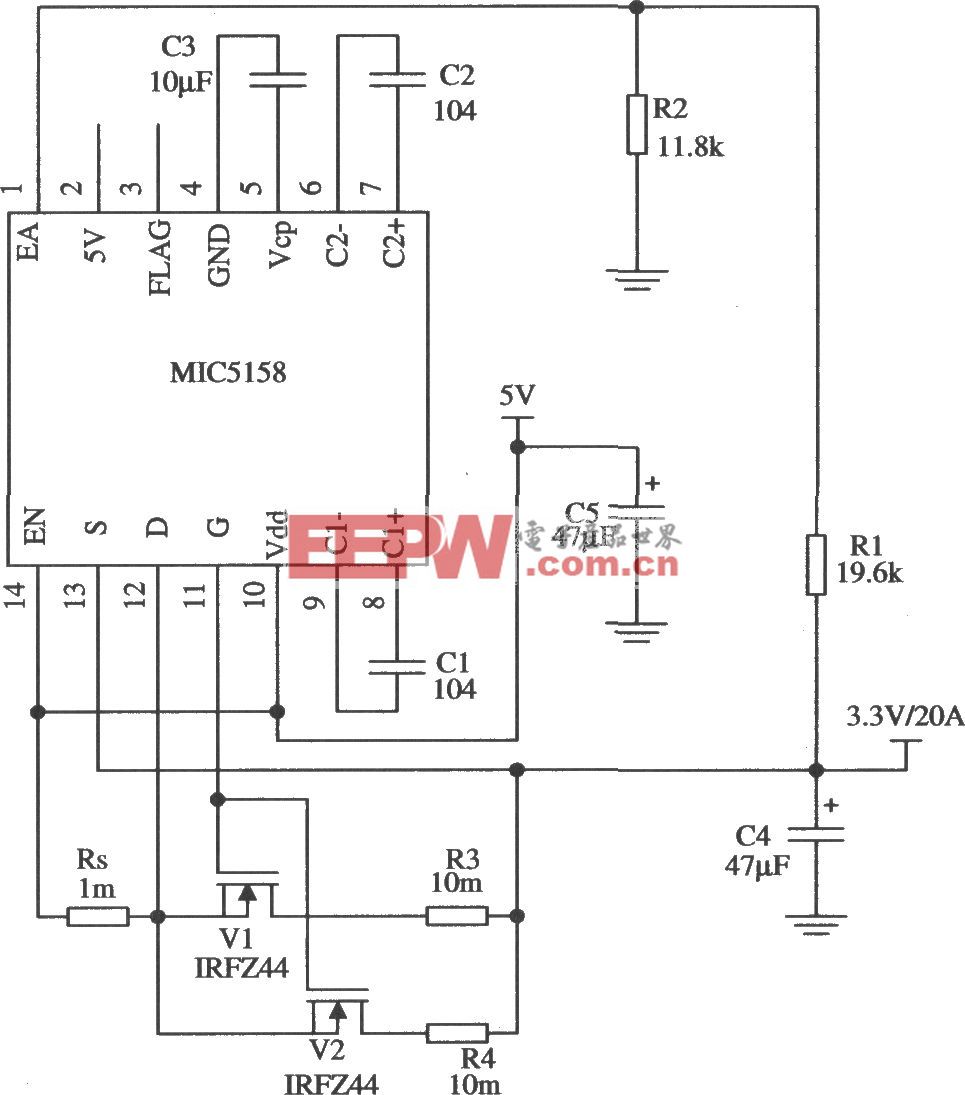

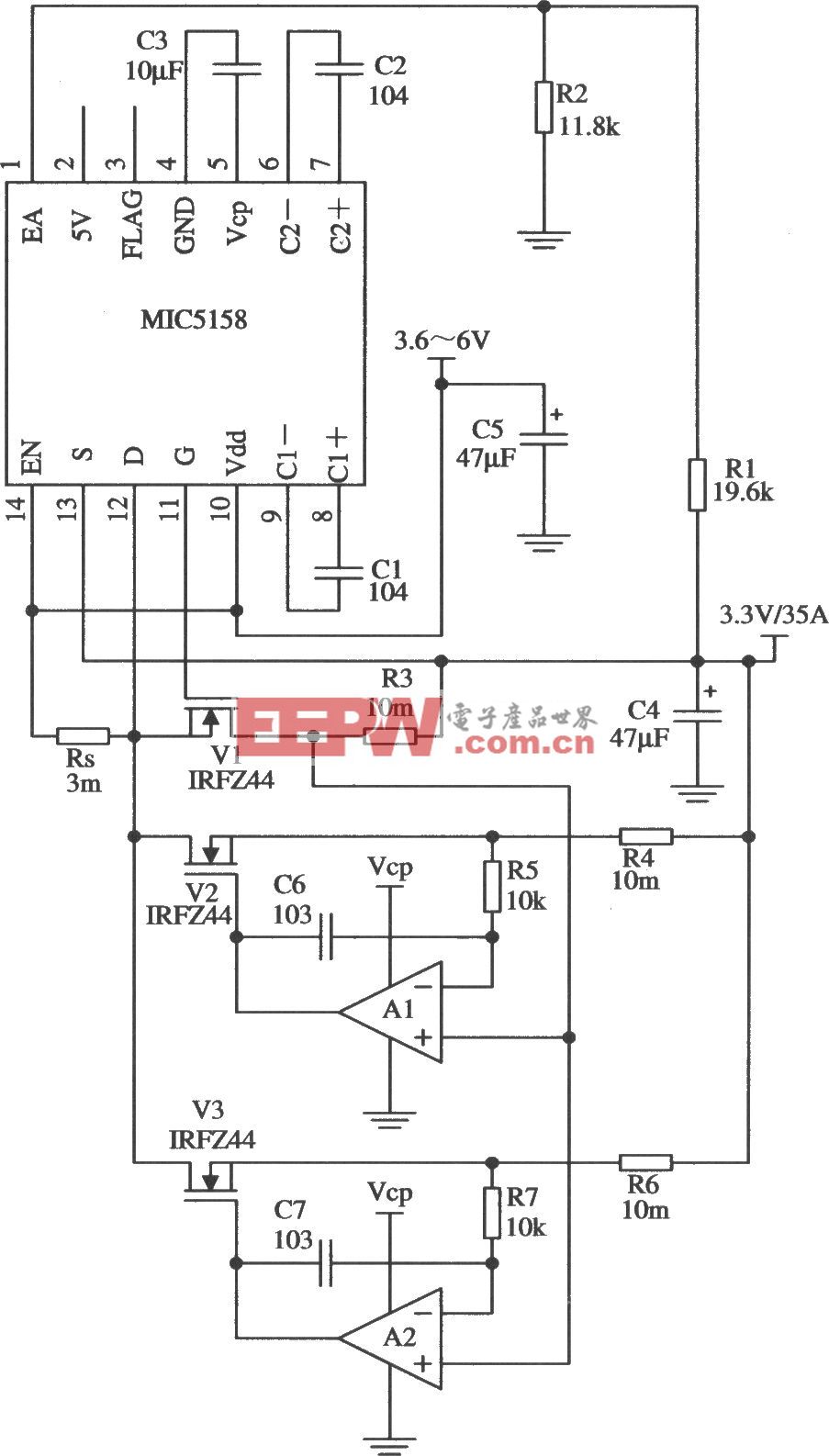

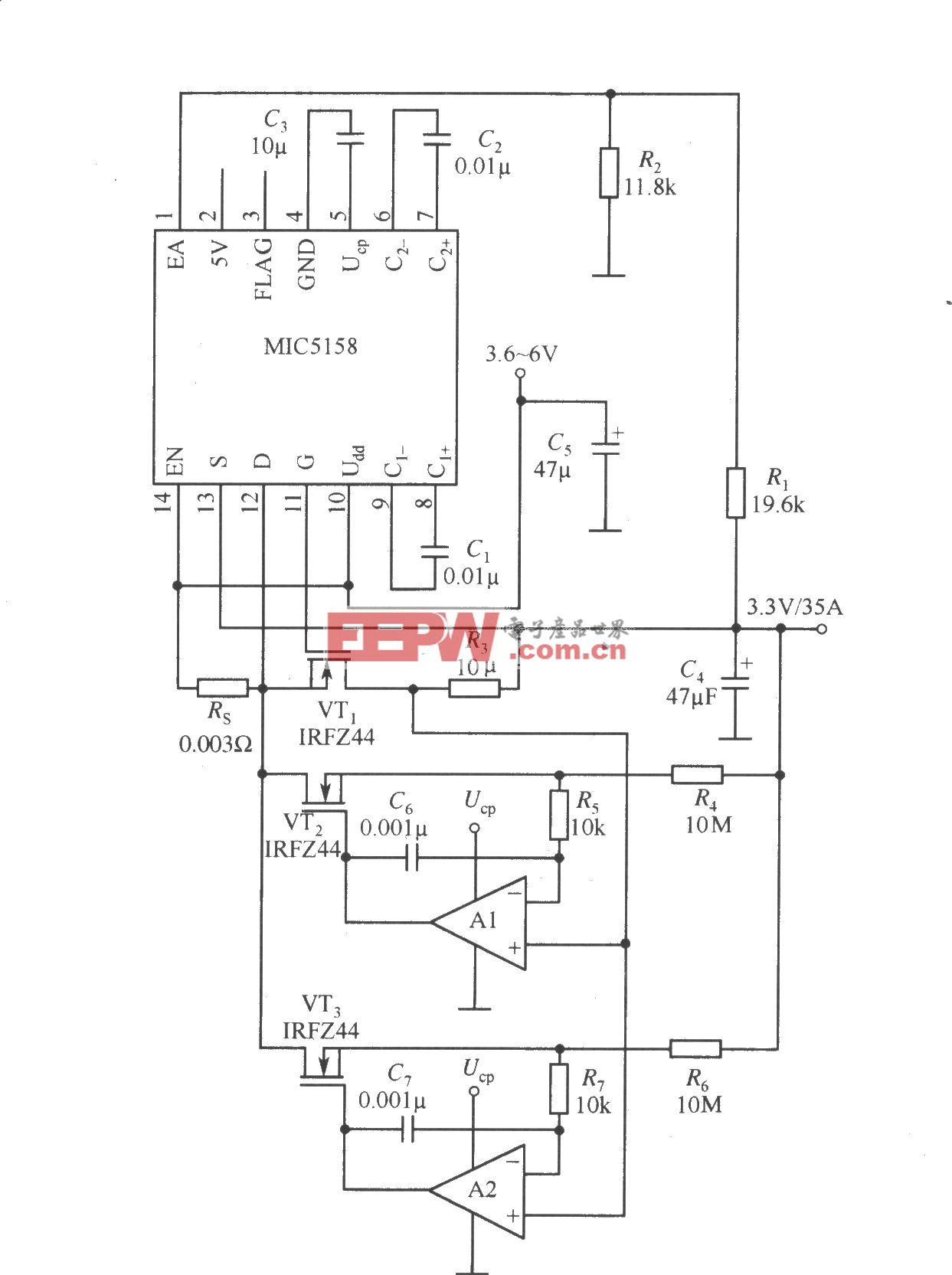

图1为Power MOSFET之安全工作区示意图,此安全区主要是由四个条件所决定:导通电阻RDSON、最大脉冲电流IDpulse、最大功率损耗PD及最大耐压VBR。正常条件下,Power MOSFET都必须工作在安全工作区域之内。

图1 Power MOSFET之安全工作区域图

2 Power MOSFET传导与并联使用

Power MOSFET的传导(transconductance, gfs)为其工作在线性区(linear region)时,VGS与ID间的小信号增益值,可以用下式表示。

gfs=ΔID/ΔVGS (2)

Power MOSFET在导通及截止的过程中工作在线性区,因此传导的大小与导通及截止的过程中,所能流经Power MOSFET的最大电流有关,亦即:

ID=(VGS-Vth)middot;gfs (3)

然而在中/高电流的应用电路中,在为了提升效率所采用的Power MOSFET并联方法下,传导值就会直接影响到在导通及截止的过程中,流经各Power MOSFET的电流均匀程度。一般而言,会采用具高传导值的Power MOSFET,减少并联使用中的电流不均情况。

3 切换速度与闸极电荷(Qg)

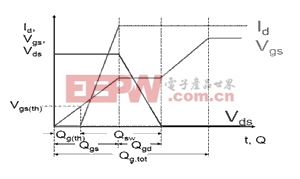

CGD充电时之VGS电压及相对应之各项波形。由图中可知,极间电容CGS及CGD在Power MOSFET的切换速度上扮演重要的角色。

Qg用以表示Power MOSFET在导通或截止的过程中,驱动电路所必须对极间电容充电/放电之总电荷量。在一般操作之下,Power MOSFET切换的延迟时间可用一简单公式表示。

td=Qg/iG (4)

此外,在驱动电路驱动Power MOSFET导通及截止的过程中,对Power MOSFET的极间电容进行充/放电的栅极电荷,事实上也是一种形式的损耗,只是发生于驱动电路。若Qg值愈大,要达到高频率操作及高速切换,则需要具较高电流能力之驱动电路。Power MOSFET之驱动损耗可以下式表示。

PDRV=VDRV×QG×FSW (5)

其中,VDRV为驱动电路之驱动电压。

4 Qgd/Qgs1与dVDS/dt

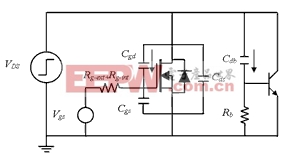

在高端MOSFET导通及低端截止的瞬间,单相同步整流降压电路架构的等效电路如图3所示。其中,输入等效电容 Ciss=Cgs+Cgd;输出等效电容 Coss=Cgd+Cds;反馈等效电容 Crss=Cgd,内含有其他寄生电容及NPN三级管。

图2 Power MOSFET栅极电荷示意图

图3 高端MOSFET导通及低端MOSFET截止过程的等效电路

在可能的操作条件下,低压侧Power MOSFET Q2截止时,且VDS上升斜率dVDS/dt很高时,VDS可能经Cgd对Cgs充电。因此,为避免因这充电现象发生而导致的高/低压侧Power MOSFET同时导通而烧毁,一般需选用(Qgd/Qgs1)《1(Qgs1表示Qgs在Vgs《Vgs(th)时的值)。另外,在高dVDS/dt的情况下,VDS可以透过另一个寄生电容Cdb触发Power MOSFET内的寄生晶体管,造成Power MOSFET的烧毁。 因此,在实际应用电路中必须尽量避免Power MOSFET超过其dV/dt值。

5崩溃及崩溃能量

Power MOSFET在VDS》BVDSS后会进入崩溃区(Avalanche),其操作如同一齐那二极管,当能量超过某一值时,会造成雪崩击穿 (Avalanche Breakdown)。在正常使用情况下,功率晶体应避免操作于此情况。在Power MOSFET的规格表中标示有“EAS”及”EAR”参数,此参数分别代表进入崩溃时,Power MOSFET能够忍受的单次脉波及重复性脉波最大能量。

单次脉冲崩溃能量:EAS=1/2×VBS×IAS×tAV

重复性脉冲崩溃能量:EAR=1/2×VBR×IAR×tAV

其中,tAV表示Power MOSFET进入崩溃时之延续时间。

雪崩击穿一般可分为两种损坏模式: (1)高能量雪崩击穿损坏,属于高电感、低电流且长时间雪崩击穿,导致积热无法及时散逸而使得Power MOSFET损坏,例如驱动马达的应用;(2)低能量雪崩击穿损坏,属于低电感、高电流且短时间雪崩击穿,导致瞬间过热无法及时散逸而使得功率MOSFET损坏,如个人计算机主机板之中央处理器(CPU)核心电源(Vcore)的应用。大部分的功率MOSFET的损坏是由于过大的能量(Electrical Over Stress;EOS)加于组件而导致过热或超出安全工作范围而引发的。

Power MOSFET损耗分析与设计趋势

以同步整流降压转换器做损耗分析,可说明目前Power MOSFET在应用电路中的各项功率损耗情况。

对高端的Power MOSFET而言,其功率损耗为:

Ploss,Q1=导通损耗+切换损耗+驱动损耗+电容性损耗,亦即:

(6)

(6)

而低端之同步整流 Power MOSFET之功率损耗为:

Ploss,Q2=导通损耗+驱动损耗+电容性损耗+本体二极管回复损耗,亦即:

(7)

(7)

从式(6)、(7)可知,Power MOSFET主要的损耗来源有三:(1)导通电阻造成导通损失;(2)闸极电荷造成驱动电路上的损耗及切换损失;(3)输出电容在截止/导通的过程中造成Power MOSFET的储能/耗能。值得注意的是,除了导通损耗以外,其余各项损耗均与Power MOSFET之极间电容或门极电荷及切换频率呈正比。亦即,若要在较高频率操作,必须选用较低极间电容或门极电荷之Power MOSFET,可以有效减少高频率下之切换损失。

而Power MOSFET发展趋势亦是以减少导通/切换损耗、快速切换为目标,使其所应用之电源供应装置,能够达到效率高、轻量化、小型化及稳定性高之产品设计目标。以下将说明现今低压Power MOSFET之发展趋势,并以Infineon Technologies公司所生产之新一代OptiMOS?为例,比较性能优劣。

评论