模数转换器(ADC)不同类型数字输出深解

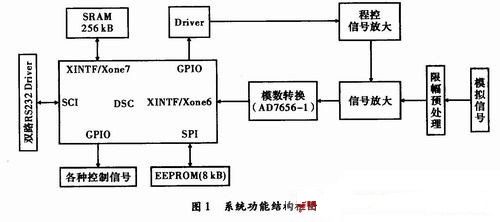

在当今的模数转换器(ADC)领域,ADC制造商主要采用三类数字输出。这三种输出分别是:互补金属氧化物半导体(CMOS)、低压差分信号(LVDS)和电流模式逻辑(CML)。每类输出均基于采样速率、分辨率、输出数据速率和功耗要求,根据其工作方式和在ADC设计中的典型应用方式进行了论述。本文将讨论如何实现这些接口,以及各类输出的实际应用,并探讨选择和使用不同输出时需要注意的事项。此外还会给出关于如何处理这些输出的一般指南,并讨论各类输出的优劣。

基本知识

使用数字接口时,无论何种数字输出,都有一些相同的规则和事项需要考虑。首先,为实现最佳端接,接收器(FPGA或ASIC)端最好使用真正的电阻终端。接收器端的反射可能会破坏系统的时序预算。使用CMOS和LVDS输出时,如果系统中有多个ADC,不要使用来自某个ADC的DCO(数据时钟输出),否则可能导致时序错误以及接收器不适当地捕捉数据。在两个ADC之间需要保持精确时序的I/Q系统中,这点尤其要注意。即使两个ADC位于同一封装中,也需要针对各ADC使用适当的DCO输出,从而保持精确的时序关系。另一个需要注意的重要参数是数据格式。必须确保ADC和接收器采用同一数据格式(二进制补码或偏移二进制)。此外,数据转换速度也很重要。随着数据速率提高,接收器能够正确捕捉数据的距离减小,原因是互连和电缆带宽限制,以及由此引起的符码间干扰等问题。这些只是为什么必须将互连视作传输线路的其中几个原因。以这种方式处理互连并了解传输线路的特性很重要。当数据速率提高时,以这种方式了解互连变得更加重要。必须确保导线尺寸正确,并且信号层与返回层之间的间距适当。此外还必须选择具有稳定介电特性的电路板材料,使得走线特性在整个互连长度上的波动尽可能小。理想情况下,传输线路可以传播到无穷远处,但在实际应用中,这显然是不可能的。集肤效应、电介质损耗和辐射损耗等因素全都会影响传输线路参数,降低信号质量。因此,必须以正确的物理参数适当设计传输线路,并且确保发送器与接收器的阻抗匹配。这样做能够节省电能,并将最高质量的信号传输给接收器。

关于CMOS,我们所需要了解的

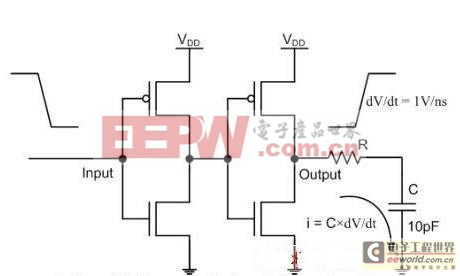

使用CMOS输出时,有多个方面需要考虑。首先考虑逻辑电平的典型开关速度(约1V/ns)、输出负载(每个门约10pF)和充电电流(每路输出约10mA)。应当采用尽可能小的容性负载,使充电电流最小。这可以利用尽可能短的走线仅驱动一个门来实现,最好没有任何过孔。此外还可以利用阻尼电阻来尽量降低充电电流。之所以必须将这些电流降至最小,是因为它们会迅速叠加。例如,一个四通道14位ADC的瞬态电流可能高达14 x 4 x 10 mA = 560 mA!串联阻尼电阻有助于抑制如此大的瞬态电流,降低输出瞬态效应产生的噪声,从而防止输出在ADC中造成额外的噪声和失真。

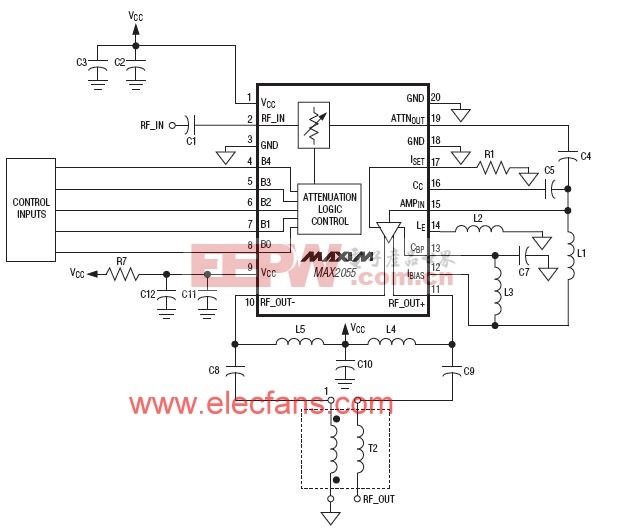

图1. 带阻尼电阻的CMOS输出驱动器

阻尼电阻和容性负载的时间常数应小于输出数据速率周期的大约10%.例如,如果使用采样速率为80 MSPS的ADC,各CMOS输出端的容性负载为10 pF,则时间常数应为12.5 ns的大约10%,即1.25 ns.因此,阻尼电阻R可以设置为100Ω,这个阻值很容易获得,并且满足时间常数条件。选择更大的R值可能会降低输出数据建立时间性能,并干扰接收器端正常的数据捕捉。ADC CMOS输出端的容性负载只能是单门负载,无论如何都不应直接连接到高噪声数据总线。要连接到数据总线,应使用一个中间缓冲寄存器,从而将ADC CMOS输出端的负载降至最低。随着CMOS输出的数据速率提高,瞬态电流也会增大,导致更高的功耗。CML的优点是:因为数据的串行化,所以对于给定的分辨率,它需要的输出对数少于LVDS和CMOS驱动器。JESD204B接口规范所说明的CML驱动器还有一个额外的优势,因为当采样速率提高并提升输出线路速率时,该规范要求降低峰峰值电压水平。

LVDS和CML

与CMOS相比,LVDS有几项优势很吸引人,包括:转换器采样速率更高而功耗更低、支持更高的数据速率、抗扰度更高以及驱动距离更长等。使用CMOS等单端信号时,印刷电路板上的噪声明显较多,这是因为CMOS输出切换感应的大量瞬态电流引起接地反弹。这种噪声更有可能耦合到ADC时钟和模拟输入中,导致SNR和SFDR性能下降。LVDS和CML采用差分信号,虽然并未完全消除CMOS中的接地反弹,但至少大大降低了这种效应。由于采用差分信号,系统本身就能抑制共模噪声,防止SNR和SFDR性能受损。LVDS和CML信号是平衡的,因此串扰被降至最小。由于信号的低压和差分性质,电磁干扰(EMI)同样降低。

提高可用带宽、改善动态范围、降低系统噪声的需求,导致转换器设计的采样速率和分辨率不断提高,因而必须使用速度更快、效率更高的数据接口。为此推出的JESD204标准利用CML技术实现其物理接口。该标准最初要求高达3.125Gbps的输出速率,这一数据速率超过了CMOS和LVDS的能力。最新版本JESD204B规定了输出数据速率高达12.5Gbps的几类转换器,CMOS和LVDS接口完全遥不可及。然而,使用差分信号虽然有这么多优势,但仍有几点必须注意。

使用LVDS和CML等差分信号

考虑任何采用差分信号的更高速接口技术时,可以应用类似的原则。事实上,数据转换速度越高,则越需要注意这些事项。对于Gbps范围内的数据速率,工艺和电路板几何尺寸变得更小,由于传输距离短得多,串扰等不良效应可能会成为问题。随着转换器采样速率和分辨率不断攀升,对更高速接口的需求是一个自然而然的结果。为此,业界首先引入了LVDS技术,尔后又推出了物理接口使用CML的JESD204接口规范。

使用差分信号时,第一件事是要确保系统正确端接。虽然接收器(FPGA或ASIC)可能有内部终端,但有时候这并不足以适当地端接系统,不采取其它措施的话,接收端数据捕捉可能会受影响。图3和图4显示了典型的LVDS和CML驱动器以及接收器所需的端接。可以使用一个差分端接电阻(RTDIFF),或者使用两个单端端接电阻(RTSE)。最终的端接电阻应约等于100Ω。使用两个50Ω单端端接电阻可以进一步抑制共模噪声,适合需要保证这一特性的应用。

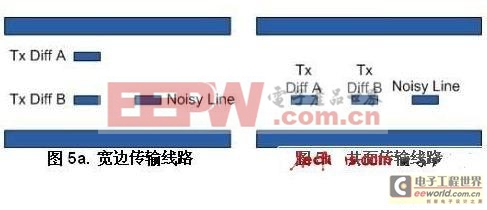

除了要求正确端接以外,还必须注意传输线路的物理布局。关于差分走线的设计,有几个常见的误解。有人说共面差分传输线路(图5a)优于宽边差分传输线路(图5b)。然而,在噪声耦合抑制方面,这两类差分传输线路均无优势可言。对于相同距离的有源传输线路,两种情况下的噪声大致相当。共面差分传输线路的优势在于设计简便且易于制造。宽边差分传输线路则更难以进行PCB布线,而且精密对准两层以保证重叠是一件很困难的事,对于电路板制造商来说比较麻烦。

图5a. 宽边传输线路。图5b. 共面传输线路

另一个常见的误解是差分传输线路必须紧密耦合才能实现最佳性能。实际上,当差分传输线路紧密耦合时,各走线的阻抗会高于所需的最佳值50Ω。此外,由于几何尺寸更小,集肤效应损耗和串扰会增加。在制造过程中,传输线路的阻抗也会变得更加难以控制。例如,假设紧密耦合的差分传输线路具有100Ω差分阻抗和5.0密尔的走线宽度,则在容差为+/- 1.0密尔的制造工艺中,阻抗偏差为+/- 10%.这一影响还要加倍,因为差分对有两条传输线路,偏差量将相当可观。不仅各传输线路的阻抗会有偏差,而且当线路分开以进入封装或连接器时,还会出现阻抗不连续现象图6显示了当差分传输线路必须分开以进入封装或连接器时,两种情况下的阻抗不连续的相对幅度差异。

紧密与松散耦合的传输线路--阻抗不连续

何种接口"最佳"?

首先需要考虑的是数据的传输速度和传输距离。一般而言,当ADC的速度和分辨率提高时,制造商会按CMOS、LVDS、CML的顺序升级,从而尽可能精确、高效地将数据从ADC传输到接收器(通常是FPGA或ASIC)。采样速率低于150-200 MSPS且分辨率低于14位的ADC一般可以使用CMOS输出。但是,当一个封装内的ADC数量增加时,CMOS输出的数量也会增加,最终会需要一个采用更少输

评论