功率芯片结合纳米技术推进功率转换技术进步

另一方面,功率芯片制造商正不断开发能够处理高电压和大电流的技术。将交流电网电压转换至中间母线需可靠的设备提供数百伏电压和数安培电流。同时,再由母线电压转换至最终负载电压则需要数百安培电流的低压设备。上述功率转换已在个人电脑上实现了,它先将线路功率因数校正(PFC)电压降至电源盒外的母线电压,再降至主板的通用低电压, 这充分展示了新的高电压和大电流半导体技术及其架构的效用。

谐波极限值和功率因数校正

当电气负载(如PC)消耗的电流与输入电压(AC线路)同相,且电流不失真(正弦波)时,交流电网的功率输出可达到最佳状态。为此,作为欧洲标准的IEC 6100-2-3规定了各类设备的谐波极限值。例如,所有消耗功率超过75W的个人电脑的谐波(度数 n=3、5、...至39) 都必须处于或低于给定的曲线(以mA/W为单位)。目前,台式机的功耗在140W至250W之间,这意味着所有销售到欧洲的PC都必须符合上述标准。当这项标准确立后,世界其它地区都将逐步按照其执行。

|

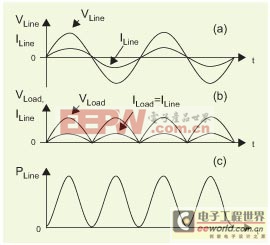

电源线路(PLINE=VLINE*ILINE)具有双倍频率 |

谐波越高, 限制越严格。但这些谐波的能量也越少,更易于滤波。根据该规范,允许谐波电流的最大输出大于600W,这样要在更高功率下符合这一规范就更具挑战性。

功率因数(PF)是与线路提供功率的综合质量相关的一个总体参数,它与输入电流总谐波失真(THD)的关系如下式所示:

PF = cos( /(1+THD2)1/2 [1]

式中(是线路电压和消耗电流间的相位差。无相位差((=0),且无失真(THD=0)时, PF=1。由于分子(cos( (在0到1之间, 而分母总是大于或等于1,因而PF (=1。

由于IEC 61000-3-2标准规定了THD的谐波分量,THD和PF因此都不足以度量性能。实际上,这一规范的度量和遵从标准为谐波失真参数,这个参数以及达到这一规范的技术一般被划分到“PFC”或“功率因素校正”的类别中。

理论上,PF表达式中的cos( 既可为正,也可为负。请记住,负的cos( 值相当于负载电路对线路供电的情形。在基于二极管桥的整流电路中,这种情形是不可能发生的。

谐波极限值规范的约束

将功率从交流电网引至负载的标准方法是直接在负载两端跨接二极管桥整流器。如以由二极管桥式整流器和阻抗负载组成的简单系统为例,桥后的电压和电流则不失真,无相位差,可整流为正弦波,且PF=1 (图1)。在这种情况下,输入到负载上的功率由倍频、零最小和瞬时值波形构成:

P(t)= (V2/R)*sen2(t = (1/2)*(V2/R)*(1-cos2(t) [2]

式中V是线路电压的幅度,R为负载,(为线路的角频率2(f,f=50Hz或60Hz。由方程[2]可得实际或平均的功率为:

PAVE=(1/2)*V2/R = VRMS2/R [3]

随时间变化的零平均脉动功率为:

PPΜLS = -(1/2)*(V2/R)*cos2(t [4]

这个简单例子描述了理想的AC线路整流电路模型。而另一方面,该电路没有能量存储功能,整流器输出端功率具有AC线路的倍频分量。在这一理想化的模型中,典型的负载实际上需要恒定(DC)功率。因此,它必须具有大容量的能量存储元件,一般采用处理非失真输入功率P(t)和DC输出功率PAVE差异的电解电容来实现。这个差异自然是由[4]所给出。

|

功率转换链高级方块图,从交流线端至中间电压总线Vbus。 |

在负载中添加一个小电容C将使通过负载的电压变得平滑,纹波减少,但由于电流波形严重偏离了正弦波并采用了目前脉冲的形状,因而使到PFC减小。连接电容的粗糙桥式整流器是IEC-61000-3-2规范制订以前,多数商业设备所采用的常规无PFC电路架构,PFC技术是在低输入谐波电流量和严格调节输出电压下,维持输入和输出功率匹配的方法。

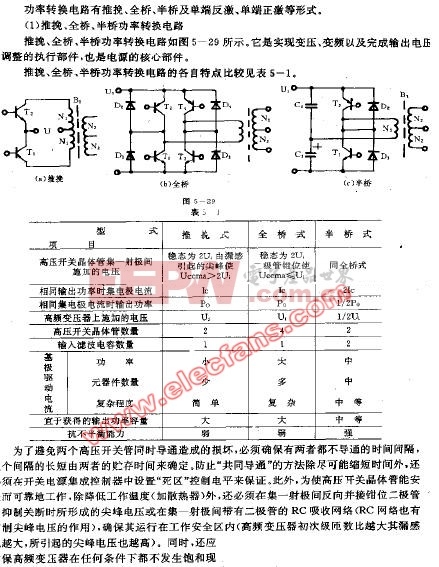

PFC架构

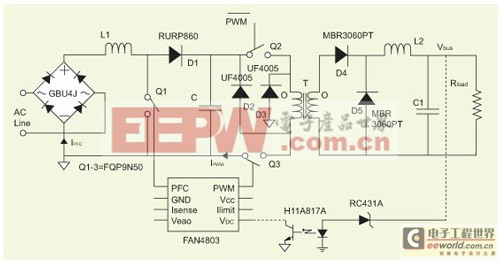

PFC的一般架构包括与AC线路接口的穚式整流器,以及PFC升级。PFC级存储着电容C (图2) 中的无功功率,然后是PWM升压级。正如前文中讨论,PFC级可实现线路电压和电流的良好匹配。

在完全平衡的条件下(PF=1),我们会发现AC线路侧的波形如图1(a)所示。而在整流侧,电容C产生的无功功率为:

PCR(-VCDC*C*2(*VCRIPPLE*cos2(t [5]

式中VCDC 为电容两端的DC电压,VCRIPPLE 为其纹波峰值,而(=2(f为线路电压的角频率(f=50/60Hz)。应注意PCR 类似于图1系统(无电容)中的PPΜLS。由方程[5]可得:

VCRIPPLE ( PCR(PEAK)/ VCDC*C*2( [6]

这是很有用的设计公式,它揭示了电容C、直流电压及纹波值之间的折衷关系。在经过PFC级线路处理后的谐波量, 通过DC/DC转换器的消除电容C的过滤,即可充分去除输入的纹波电压。

PFC和PWM的实现

图2中的控制是组合IC器件,它是非常小巧的芯片,在电路板上集成了两个控制环路。PFC部分是由电感L1、开关Q1 (MOSFET)、大电容C和二极管D1构成,这是受控于PFC/PWM控制器的一半电路。然后通过“前向”转换器将C上的电压调节至总线电压。组合IC的另一半用于初级控制,其中包括开关Q2和Q3、二极管D2-D5、无源元件L2和C2,电压参考IC用于次级控制。该转换需要隔离高输入和低输出电压,通过正向转换通道的变压器(T)和反馈通道的光耦来实现隔离。

|

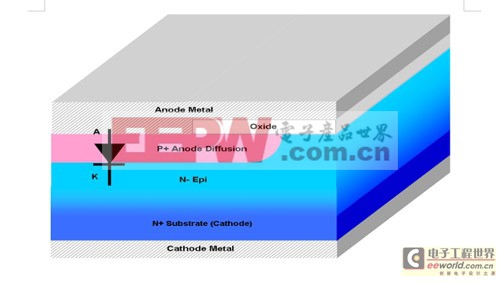

图3. 升压二极管器件的剖面图 |

控制器架构

控制器由主变压器(T)供电(Vcc引脚),即辅助次级绕组变压器(图中未标明)产生一个相对较低的电压(15V)。由于每个控制器I/O引脚的电压都低于15V,因此该芯片采用低压密集型BiCMOS工艺。当PFC和PWM两部分的运作协调有效时,可以最低的成本(BOM)实现PFC和PWM功能。PFC部分通过上升沿调节控制。MOSFET Q1在时钟边缘关断,并根据PFC方波的前导/上升沿,在环路控制下导通。PWM用“拖尾”调制进行控制。MOSFET Q2在时钟边缘导通,并根据PWM方波的拖尾/下降沿,在环路控制下关闭。相应地,在同步时钟的作用下,两个晶体管决不同时消耗电流,这样进一步重新分散电流,从而使高电压输入电容的数值降至最小。请注意,在50Hz时,波型与图1中的曲线类似,当时钟频率为67KHz时,开关调节器的限幅波形使电流出现纹波。

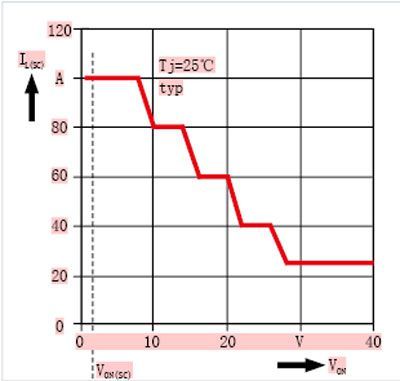

离线功率晶体管

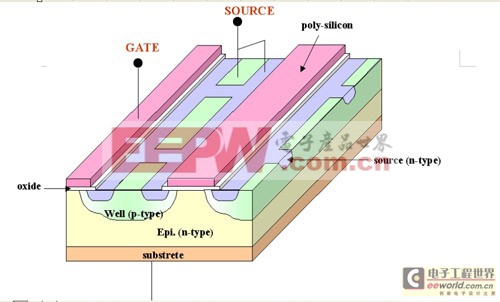

线路与变压器基层之间的所有二极管及DMOS开关均为高压器件。IEC 61000-3-2规定单相供电线路中的电压最大不超过240VRMS(三相线路最大为415VRMS)。因此,这些元件可承受400V至1000V电压。图3的升压二极管的反向电压高(600V),正向压降小(8A时为1.5V),它是超快速的恢复整流器(trr60ns)。它的玻璃钝化离子注入外延结构如图3所示。其它高压元件为可承受600V电压的超快速ΜF4005续流二极管和开关Q1-3。它们都是采用平面条纹DMOS工艺制造的500V N沟道增强型MOSFET,开关速度高,开态电阻非常低(在10V VGS下的开态电阻为0.73()。

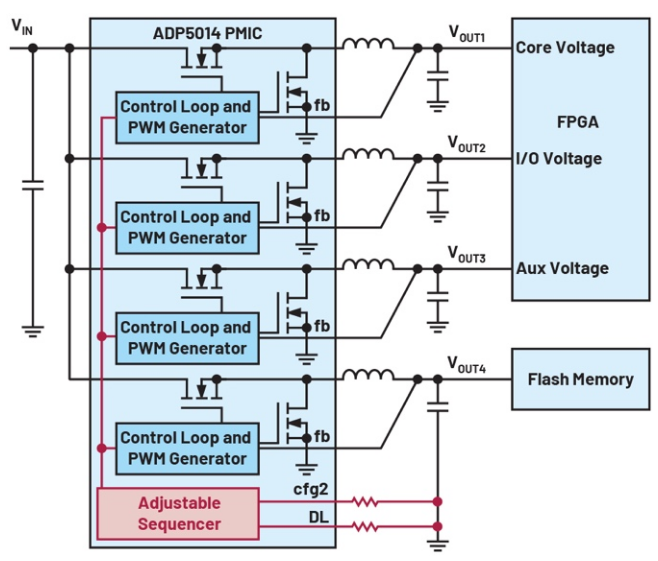

转换为低电压的DC-DC转换

总线电压VBΜS (如12V)通过开关调节器(一般为同步降压转换器)分配和降低,将电压降低为常用的3.3V、2.5V、1.8V或VCPΜ。达到50A负载的理想上升沿波谷控制结构是两相交替同步降压转换器,每相的开关频率可达1MHz。该IC可直接驱动分立DMOS晶体管的高边和低边,其集成驱动器的阻抗低(1欧)。

|

图4. 高压DMOS晶体管的剖面图 |

未来趋势

有源功率因数校正的方法容易满足IEC 6100-3-2的功率因数规范,但所需元件太多。先进的组合IC在同一裸片上集成了两个控制器,从而降低了半导体元件的复杂度。然而,这两个控制器是截然不同的,各自需要一套完整的无源元件来实现相关功能。因此,未来的理想器件是真正的单级PFC/PWM控制器,它可将复杂性降低一半或以上,而且不会影响性能。PFC/PWM功能的集成仍处于初发阶段,未来将出现完善的新型架构,可大幅削减现有方案的物料费用。

就功率分配的发展趋势而言,即从VBΜS至低压的DC/DC转换,目前的主流架构是采用交替的同步降压转换器,未来的挑战是: 采用能够快速响应负载变化的架构,以减少输出电容数量。人们需要在这些领域开展许多研究工作,这类技术的突破对于整个功率转换市场都是非常重要的。

评论