用ADS实现一个2.38GHz全集成化低噪声放大器设计

目前,在高达数GHz的RF频段范围内,广泛使用的是GaAs MESFET LNAs,其优点是能够在功率增益高达20 dB的同时,使噪声系数低至大约1 dB。但随着CMOS电路技术的成熟,近来对RF CMOS电路元件的研究成果越来越多,在无线通信系统上也已经实现了SoC化。如果CMOS制造技术能克服噪声大,功率损耗大等缺点,凭借其低廉的价格,CMOS LNAs将有可能在数GHz的RF频段范围内,逐渐取代GaAs MESFET LNAs。

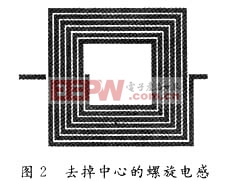

由于LNAs通常位于整个接收电路的第一级,由式(1)可以看出,第一级的LNAs对于接收电路有很大的影响。所有在设计LNA电路时,应考虑降低噪声,提高增益,输入输出阻抗匹配,降低功率损耗,提高线性度等重要因素。

![]()

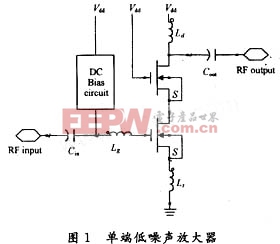

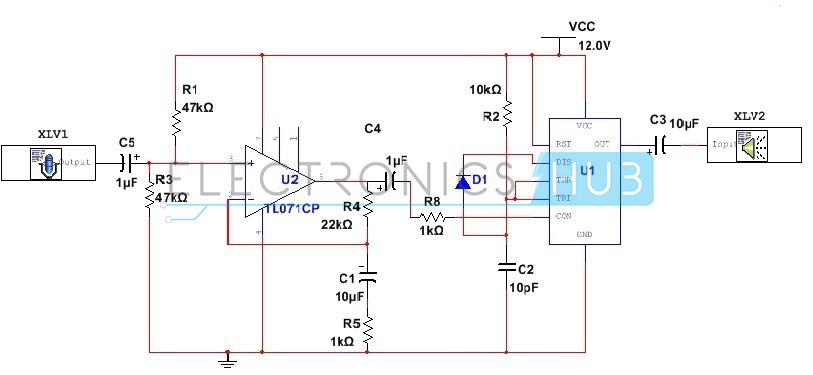

如图1所示,设计一个cascode型输入的低噪声放大器。图中Ls及Lg用来实现输入阻抗匹配,而调整Ld和Cout可以实现输出阻抗匹配。Cin可以用来阻止输入端的直流信号。

对于放大器的输出,由于放大器使用LC并联电路作为负载,所以当LC谐振在2.38 GHz时,理想的LC电路应呈现出开路状态,此时负载最大,增益也最大。但是电路的增益仍然受到电感和电容的Q值影响,所以在进行软件仿真时还需通过调整电感电容值来调整LNA的中心频率。

3 本LNA中无源器件的结构

由于此设计采用全集成化设计,所以无源器件都用CMOS工艺制作在芯片内部,即内嵌式(on-chip)。

3.1 电感结构

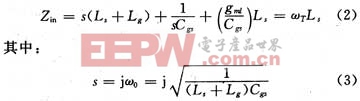

此电路中电感采用内嵌式螺旋电感。采用内嵌式电感可以节约面积,提高电路集成度,但是却牺牲了Q值,并且在CMOS工艺中电感的制备比较难以控制,所以在实际layout时将螺旋电感的中心拿掉,因为越接近核心,电荷密度越大,但核心部分对电感值的贡献不大,中心去掉不会对整个电感有太大影响,还可以提高Q值。

此电路中采用MIM(metal-insulator-metal)电容,是平板电容的一种变形,如图3所示。这种电容的好处是容值较为固定,并且结构简单。相比一般平板电容,在上下级板中间多了一层CTM(Capacitor TopMetal)层,可以通过缩短两极板之间的距离来提高容值或缩小电容所占面积。

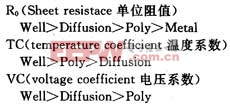

在当前的CMOS工艺中,根据不同的材料和制备工艺,常用的电阻有Well电阻、Poly电阻、Diffusion电阻和Metal电阻。各种电阻的导电层特性如下:

4 仿真设计

(1)确定设计目标。本文中电路工作在蓝牙系统中,工作频率为2.38 GHz,设计一个超低噪声以及超高增益的LNA电路。

(2)设计电路结构。本电路基本结构为cascode单级放大电路,再加上一些周边的匹配电路和电压偏置电路来构成LNA电路。

(3)本文使用安捷伦的ADS系统来做高频仿真,使用0.25μm的RF模型。主要仿真S参数、噪声系数、线性度、功率增益等LNA电路的重要参数。

(4)根据0.25μm制造工艺的layout规则来设计电路中的各个元件,并且尽量做到电路对称。

5 仿真结果

本文电路使用0.25μm制造工艺,电源电压2.5 V,工作频率2.38 GHz的全集成化单端LNA电路。

5.1 S参数仿真

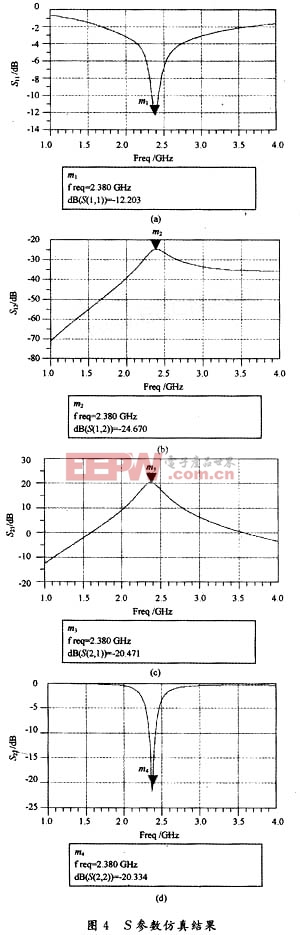

图4是此电路在ADS中的仿真结果,图4(a)中S11是电路输入反射系数,为-12.203 dB;图4(b)中S12为电路的隔绝度(isolation),避免LNA下一级的反射信号影响到LNA输入端的信号,本电路中为-24.67 dB;图4(c)中S21表示电路的功率增益,其值为20.47 dB;图4(d)中S22为输出反射系数,大约为-22.33 dB。

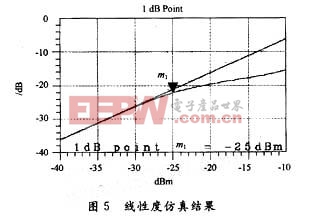

一般来说,一个系统的线性度越高越好,但是电路中含有晶体管等非线性有源器件,所以在LNA电路工作在较高功率时,输出会产生非线性失真。在仿真时,为了表示线性度,定义出一个1 dB点,表示输出相比输入压缩了1 dB。由图5中可以看出,1 dB点出现的越靠后,说明线性度越好。本电路仿真出的1 dB点在-25 dBm的位置。

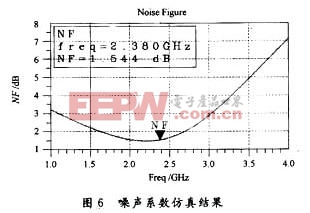

噪声系数是关系到一个放大器性能好坏的重要参数,其定义为输入信噪比和输出信噪比的比值:

![]()

6 结语

设计射频电路的LNA,在开始设计的时候就要考虑很多因素,例如为了提高增益,便要增加功率消耗,为了与下一级耦合,可能会影响整个LNA性能。通过综合的平衡,才能设计出满足不同性能需求的低噪声放大电路。本文设计的电路,在提供20 dB高增益的同时,只有1.5 dB的噪声系数,达到了设计要求。

电子管相关文章:电子管原理

评论