工程师:基于多层板PCB设计时的EMI解决方案

电源汇流排

本文引用地址:http://www.amcfsurvey.com/article/227023.htm在IC的电源引脚附近合理地安置适当容量的电容,可使IC输出电压的跳变来得更快。然而,问题并非到此为止。由於电容呈有限频率响应的特性,这使得电容无法在全频带上生成干净地驱动IC输出所需要的谐波功率。除此之外,电源汇流排上形成的瞬态电压在去耦路径的电感两端会形成电压降,这些瞬态电压就是主要的共模EMI干扰源。我们应该怎麽解决这些问题?

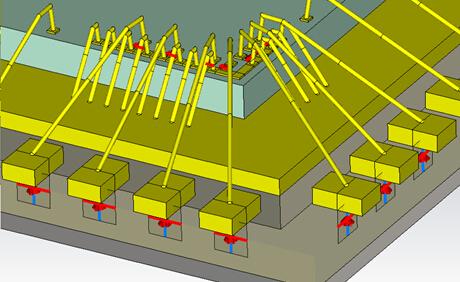

就我们电路板上的IC而言,IC周围的电源层可以看成是优良的高频电容器,它可以收集为干净输出提供高频能量的分立电容器所泄漏的那部份能量。此外,优良的电源层的电感要小,从而电感所合成的瞬态信号也小,进而降低共模EMI。

当然,电源层到IC电源引脚的连线必须尽可能短,因为数位信号的上升沿越来越快,最好是直接连到IC电源引脚所在的焊盘上,这要另外讨论。

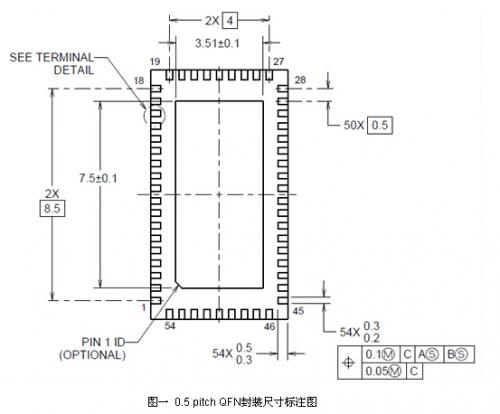

为了控制共模EMI,电源层要有助於去耦和具有足够低的电感,这个电源层必须是一个设计相当好的电源层的配对。有人可能会问,好到什麽程度才算好?问题的答案取决於电源的分层、层间的材料以及工作频率(即IC上升时间的函数)。通常,电源分层的间距是6mil,夹层是FR4材料,则每平方英寸电源层的等效电容约为75pF。显然,层间距越小电容越大。

上升时间为100到300ps的器件并不多,但是按照目前IC的发展速度,上升时间在100到300ps范围的器件将占有很高的比例。对於100到 300ps上升时间的电路,3mil层间距对大多数应用将不再适用。那时,有必要采用层间距小於1mil的分层技术,并用介电常数很高的材料代替FR4介电材料。现在,陶瓷和加陶塑料可以满足100到300ps上升时间电路的设计要求。

尽管未来可能会采用新材料和新方法,但对於今天常见的1到3ns上升时间电路、3到6mil层间距和FR4介电材料,通常足够处理高端谐波并使瞬态信号足够低,就是说,共模EMI可以降得很低。本文给出的PCB分层堆叠设计实例将假定层间距为3到6mil。电磁屏蔽

从信号走线来看,好的分层策略应该是把所有的信号走线放在一层或若干层,这些层紧挨著电源层或接地层。对於电源,好的分层策略应该是电源层与接地层相邻,且电源层与接地层的距离尽可能小,这就是我们所讲的“分层"策略。

多电源层的设计

如果同一电压源的两个电源层需要输出大电流,则电路板应布成两组电源层和接地层。在这种情况下,每对电源层和接地层之间都放置了绝缘层。这样就得到我们期望的等分电流的两对阻抗相等的电源汇流排。如果电源层的堆叠造成阻抗不相等,则分流就不均匀,瞬态电压将大得多,并且EMI会急剧增加。

如果电路板上存在多个数值不同的电源电压,则相应地需要多个电源层,要牢记为不同的电源创建各自配对的电源层和接地层。在上述两种情况下,确定配对电源层和接地层在电路板的位置时,切记制造商对平衡结构的要求。

总结

鉴於大多数工程师设计的电路板是厚度62mil、不带盲孔或埋孔的传统印制电路板,本文关於电路板分层和堆叠的讨论都局限於此。厚度差别太大的电路板,本文推荐的分层方案可能不理想。此外,带盲孔或埋孔的电路板的加工制程不同,本文的分层方法也不适用。

电路板设计中厚度、过孔制程和电路板的层数不是解决问题的关键,优良的分层堆叠是保证电源汇流排的旁路和去耦、使电源层或接地层上的瞬态电压最小并将信号和电源的电磁场屏蔽起来的关键。理想情况下,信号走线层与其回路接地层之间应该有一个绝缘隔离层,配对的层间距(或一对以上)应该越小越好。根据这些基本概念和原则,才能设计出总能达到设计要求的电路板。现在,IC的上升时间已经很短并将更短,本文讨论的技术对解决EMI屏蔽问题是必不可少的。

评论