改善高速IC比较器瞬态响应肖特基二极管的电路设计

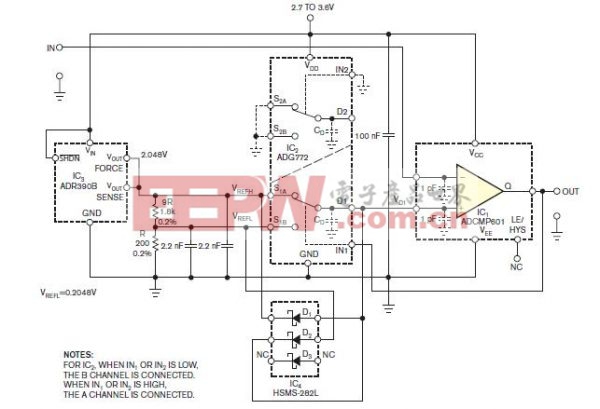

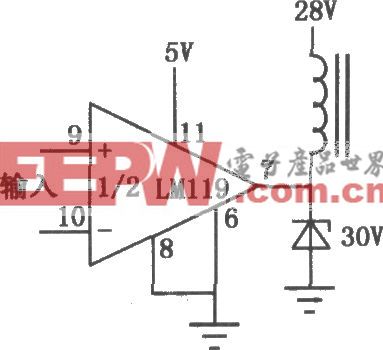

在设计实例中,一条电路把精确DC基准电压切换到高速IC比较器的非逆变输入端。该电路使用一个先断后连(BBM)方式工作的2 : 1多路复用器。多路复用器有寄生电容,后者向多路复用器的D1漏极注入的电荷QD1INJ可能会导致比较器的基准输入端出现误差电压(图1)。以下方程定义了峰值误差电压的近似值:

本文引用地址:http://www.amcfsurvey.com/article/226751.htm

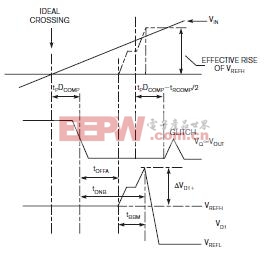

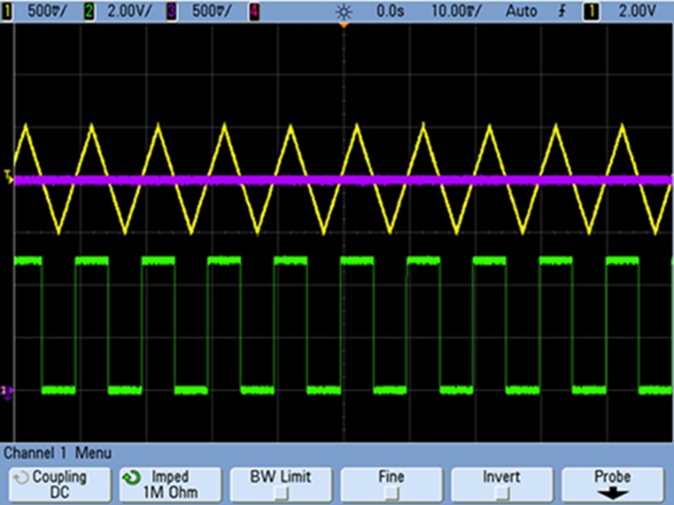

图1,电荷注入可能会在电压比较器的输出端中产生毛刺,并且这些毛刺可能导致逻辑隐患。

其中CD1OFF是IC2的D1端子的电容,CIN(约为1 pF)是比较器的输入电容。IC2的BBM间隔约为3ns,而Analog Devices公司ADCMP608和ADCMP609比较器的信号传播延时是该值的10倍。因此,它们无法在3ns内改变自己的状态。Analog Devices公司的同一产品家族中有速度为10倍的零件,即ADCMP601和ADCMP602。遗憾的是,这些器件能感觉到这些尖峰。高电平基准电压VREFH的电压偏移会导致输出电压的突然短期上升。

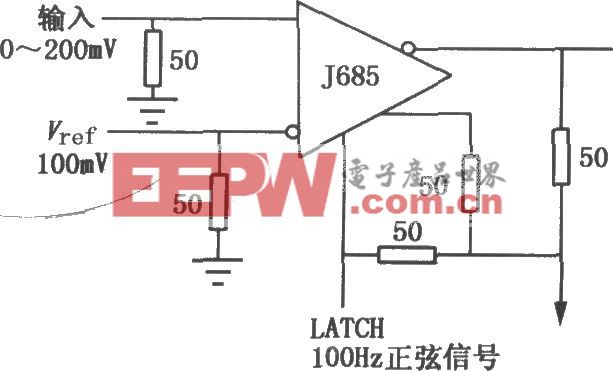

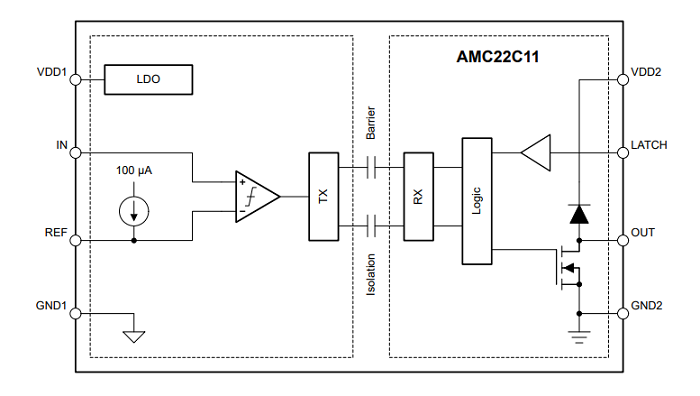

当高基准电压超过比较器逆变输入端的电压时,它的输出再次变高,即产生毛刺。当比较器穿越理想电平时,比较器的输出经过延时后变低。正误差电压开始演变,并具有额外延时,长度为IC2的通道A的关断时间。ADCMP601的数据表显示的是电荷注入源极。但在此情形下,电荷注入漏极在起作用。作为粗略估算,你可以使用参考文献2中的电荷注入数据。当电荷注入过程改变符号时(这取决于共模电压的值),VD1处的电荷约为0.8 pC,它等于高电平基准电压,并且当基准电压为低电平时,它约为–0.3 pC。该电压终止时,延时等于模拟开关IC2(是ADG772)中各通道的接通时间。比较器的输出端无意中返回高电平,虽然历时不超过5ns,但可能导致某些逻辑电路意外响应。当负斜率的输入斜坡穿越较低的基准电压时,也可能会出现类似情况。为防止这些危险状态,你可以添加两只肖特基势垒二极管(图2)。只要D1端子出现正电压偏移,比高基准电压高约200mV,则二极管D1就开始导电,而D2在电压偏移比低基准电压低200mV时导电。而且,这些二极管的非线性结电容随正向电压一起上升,从0V正向电压时的0.7pF升至100mV正向电压时的大约1.05pF。输入电压接近高基准电压时,二极管D2被逆向偏压将近2V,并且其电容降至大约2/3CD(0),其中CD是未偏压二极管的电容。二极管D1和D2的总电容为1.5 pF。该数值会使输入电容增加。由于电荷注入未超过0.8pC,因此D1端子处的电压偏移小于160mV。二极管D1和D2位于二极管三件组合IC4(Avago Technologies公司的HSMS-282L,参考文献4),但你还可以使用一颗双二极管IC。

图2,肖特基势垒二极管D1抑制比较器IC1的非逆变输入端出现的正电压尖峰(它们在输出电压由高至低的瞬变之后立即出现)。二极管D2使基准电压在输出电压由低至高瞬变期间出现的负偏移保持在一定范围。

评论