芯片-封装协同设计方法优化SoC设计

随着工艺节点和裸片尺寸不断缩小,采用倒装芯片封装IC器件的消费电子产品的数量日益增加。但是,倒装芯片封装制造规则还没有跟上工艺技术发展的步伐。

因此需要一种更精确、更高效的I/O接口设计方法,特别是针对倒装芯片设计的I/O接口设计方法。这种一体化芯片-封装协同设计方法应允许开展早期的可行性研究,还要能优化封装和芯片接口设计,同时能满足芯片和封装需要的严格约束条件。

目前,大多数倒装芯片设计公司都采用内部方法进行倒装芯片规划。这种方法主要利用电子表格捕获和存储设计输入和约束。公司自己开发脚本处理电子表格中的数据,并产生指令去指导设计实现。这种方法通常是从一个简单的系统开始,然后随着设计复杂性的提高,逐渐发展成为一套复杂的格式和脚本。

这种方法有许多缺点。首先,这种系统的维护费用昂贵并会降低设计师的产能。第二,电子表格在设计描述方面有很大的局限性。第三,脚本缺乏综合能力,无法执行假设分析,也无法对设计进行成本、性能和可靠性方面的优化。第四,基于电子表格和脚本的系统不能精确预测设计的最终实现。

协同设计环境

随着裸片的不断缩小以及I/O数量和速度的不断提高,芯片和封装之间的接口很快成为了设计中约束最严格的部分。能够及时并且同时设计出高质量和低成本的封装与芯片可以实现完全不同于普通或故障芯片的成功产品。

因此需要一种一体化的芯片-封装协同设计系统,这种系统要使用工业标准的数据库OpenAccess,并能与第三方封装和接口实现工具相接。这种一体化设计环境能让设计师在单个数据库中查看和操作芯片与封装数据。由于设计数据库包含了完整的封装和芯片实现数据,这种数据库可以同时供芯片和封装设计小组使用。

Tcl接口允许用户开发Tcl脚本来探测设计数据,产生数据报告,并实现设计流程的自动化。通过使用数据库或LEF/DEF等标准接口还可以在协同设计环境和第三方芯片与封装实现工具之间实现数据交换。

高效的封装和芯片协同设计解决方案必须具有快速建立原型的能力,因为需要在设计周期早期就做出封装决策,此时设计网表和/或物理库还没有准备好。预测最终实现的精度也很重要。如果没有足够的精度,在原型设计或规划阶段做出的设计决策可能导致实现困难,从而严重影响出带时间。

保守的规划可能不必要的增加封装成本。协同设计系统需要允许用户开发出多种场景来让设计师测试不同的封装方案。有了这种功能后,用户可以用不同的基底堆叠方法建立原型设计,并通过可行性检查找到最便宜的封装解决方案。

任何设计参数变化都是递增的,设计可以用修改后的设置自动更新。例如,如果用户想试验具有较少层数的基底、或较小BGA、或不同比例的I/O焊盘单元,用户可以在短短几分钟内导入/产生一种新的基底堆叠方案,或产生另一个BGA,或建立一套新的I/O单元原型。不同的设计解决方案可以保存为独立的数据库供比较和设计审查。还可以从可行性和成本方面对每种设计进行评估。

任何规划工具需要与最终实现有很好的相关性。一个规划只有能够顺利地实现才是完美的。在采用传统方法时,封装版图设计师必须用手工方式确认封装的可布线性。这样做将延长项目时间,并增加用于评估的封装数量。

集成化的芯片-封装协同设计环境应包含自动化的封装可行性布线器,用于对许多封装进行快速和精确的评估。这种封装可行性分析是减少设计小组与封装供应商之间工程反复的关键。

由于大多数封装修改和确认可以在同一个封装-芯片协同设计环境中完成,因此详细的封装版图只是在最终的版图实现和验证时才需要。

如今大多数倒装芯片设计依赖于以前人们熟知的良好凸点图案。这种“一成不变”的解决方案可能导致严重的过度设计,并且增加不必要的封装成本。

集成式的倒装芯片封装协同设计解决方案,提供从自动到完全定制的一整套创建功能。它能自动综合在所选封装中可布线的凸点覆盖宏(bump-cover macro),并满足SPG(信号到电源和地)约束条件,还能从文件格式导入定制的凸点覆盖宏。

此外,稳固可靠的版图编辑器能让用户在GUI中直观地创建和编辑凸点覆盖宏。在具有凸点覆盖宏库的情况下,系统可以为设计选择最佳的宏,从而实现更小的裸片面积、更少的封装布线层以及更好的电源与地分布。

这种系统中使用的综合方法可以确定最优的凸点版图,形成最高性价比的解决方案,并满足最严格的约束条件。

集成式芯片-封装协同设计规划环境的一个最重要优点是,它能同时从封装和芯片的角度考虑约束条件。当约束中存在冲突时,工具需要作出智能仲裁。

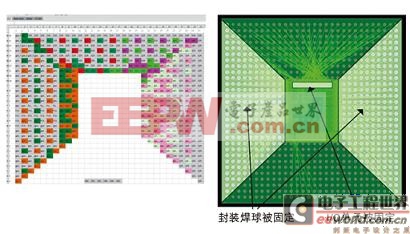

在图1所示的设计例子中,裸片正在向新技术移植,现有封装接口需要尽可能多地得到再利用。在本例中,上述封装球分配可以从电子表格中得到,其中封装东侧和西侧的球分配是固定的,它们到PCB的接口将被再利用。

图1:带有固定封装和芯片约束的裸片移植样例

评论