基于FPGA的视频监控/安全系统实现解决方案

视频监控和安全行业正在经历着一场巨大的变革,正在从传统的模拟闭路电视摄像机向基于逻辑的数字摄像机的方向发展。更高的视频分辨率、图像信号处理、先进的视频分析、多摄像系统和数字视频压缩的发展趋势推动了这一转变。其结果是,在视频监控摄像机和数字视频录像机(DVR)设计中出现了新的挑战,包括增加使用CMOS传感器、网络IP摄像技术、增加系统的集成功能、更小尺寸的外形因子、采用先进的编解码器以及增加DSP功能。

由于视频监控/安全市场的多样性和竞争性,制造商往往很难在他们自己的产品中添加差异化的功能,使其产品有别于竞争对手的产品。因此,相似的摄像机和DVR产品非常普遍。然而,上面提到的趋势为视频安全/监控原始产品制造商创造了新的机会,可以实现产品的差异化。

满足这些应用的要求需要额外的处理能力。目前的数码摄像机利用DSP芯片、专门的ASSP或ASIC来提供处理功能,但这些方案存在一些挑战。采用DSP芯片经常会出现性能瓶颈,因为这些芯片通常用串行方式处理图像信号处理任务。ASSP可能提供更多的性能,但往往是以设计的灵活性为代价。ASIC有更多的性能优化,但产量不够大,无法验证ASIC开发所需的费用和时间。设计人员需要一种灵活的方法,针对不同的细分市场提供从低端摄像机/DVR到高端应用所需的计算能力。

实现方案的选择

视频监控系统可分为两大类:摄像系统和DVR系统。摄像系统可整合单个摄像机或多个摄像机。有些系统则整合了DVR与单个摄像机或多个摄像机。

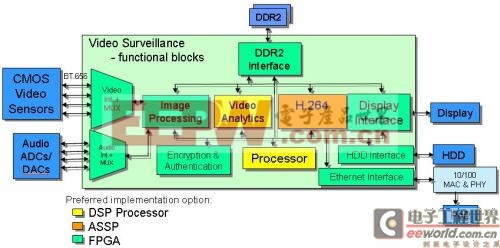

图1:多摄像机的DVR视频监控系统框图。

图1是一种通用的多摄像机的DVR视频监控系统。视频源来自CMOS视频传感器、CCD视频传感器或模拟视频源。专有的视频接口将输入视频流转换成普通的格式,然后对不同的视频流(以及音频)进行多路复用,在图像信号处理单元进行预处理。视频预处理的目的是降低噪声和消除像素缺陷。

视频分析技术应用于检测在预定义画面中的运动。这个运动检测输出可减少所需的存储容量。在一些视频监控应用中,视频分析是必需的,如人/车统计、汽车的车牌号码识别和/或人脸识别。

一个典型的具有多个摄像机视频源的视频监控系统总是会生成大量的数据,因此减少所需的存储容量非常重要。MPEG-4、H.264、和MJPEG被用来减少所需的存储容量。H.264是一种针对视频监控应用的流行压缩算法,因为它能以相当低的比特率(只有MPEG-2或MPEG-4第2部分一半或更低的比特率 )提供良好的视频质量的功能。

经过压缩后的数据通过硬盘驱动器接口存储至视频存储服务器,或通过以太网网络发送。视频数据传送到显示器之前通常是取自硬盘驱动器,并经过了解码以及一些图像后处理,如缩放、色彩空间转换或覆盖应用。通常情况下,存储器接口(如DDR2)是用来存储视频帧。此外,某些系统要求视频内容的实时加密以确保安全和源/用户身份验证。最后,需要用处理器控制和协调/排定各种不同的任务。

图2:根据吞吐量、灵活性、批量和形状因子要求进行选择的步骤。

图2说明了系统的要求,如吞吐量、灵活性、预计批量和形状因子是如何推动不同的实现技术和器件的。对于低数据吞吐量的要求,DSP处理器是最节省成本的器件。然而,产品寿命期间的预计批量以及硬件的灵活性会大大响设计者在ASIC/ASSP和FPGA器件之间作出选择。如果是硬件灵活性低的系统要求和预计有大的批量,设计者则青睐于ASIC/ASSP解决方案;而对于硬件灵活性高的系统要求和较小的预期批量,设计者青睐FPGA解决方案。常见的小型视频监控摄像机有小尺寸的要求,设计者青睐采用非易失性FPGA ,因为它们不需要额外的外部非易失性配置存储器件。

评论