基于VHDL的多功能可变模计数器设计方案

0 引 言

随着电子技术、计算机技术和EDA技术的不断发展,利用FPGA/CPLD进行数字系统的开发已被广泛应用于通信、航天、

QuartusⅡ是Altera公司在21世纪初推出的FPGA/CPLD集成开发环境,是Altera公司前一代FPGA/CPLD集成开发环境Max+PlusⅡ的更新换代产品,其界面友好,使用便捷,功能强大,为设计者提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程。

计数器是数字系统中使用最多的时序电路之一,不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。可变模计数器由于计数容量可以根据需要进行变化,为其广泛使用创造了便利。这里在QuartusⅡ开发环境下,用VHDL语言设计了一种具有清零、置数、使能控制、可逆计数和可变模功能的计数器。

1 基本可变模计数器设计

可变模计数器是指计数/模值可根据需要进行变化的计数器。电路符号图1所示,clk为时钟脉冲输入端,clr为清零端,m为模值输入端,q为计数输出端。

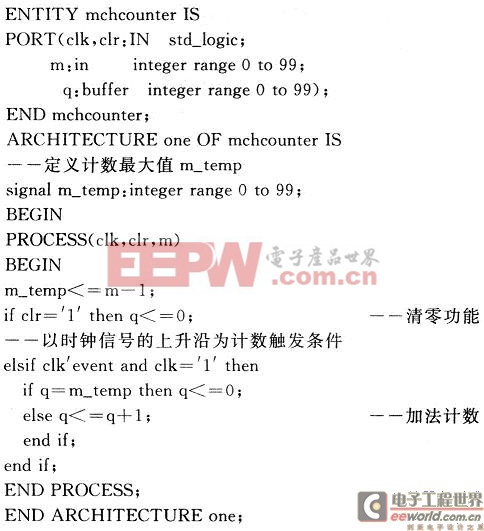

基本可变模计数器的VHDL代码如下所示:

说明:上述代码设计采用了常用的if语句结构,即“if条件句then顺序语句elsif条件句then顺序语句else顺序语句end if”结构,实现模值小于99的可变模计数。

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论