对FIR数字滤波器的FPGA实现的研究

如今,FPGA已成为数字信号处理系统的核心器件,尤其在数字通信、网络、视频和图像处理等领域。现在的FPGA不仅包含查找表、寄存器、多路复用器、分布式块存储器,而且还嵌入专用的快速加法器、乘法器和输入,输出设备。FPGA具有实现高速并行运算的能力,因而成为高性能数字信号处理的理想器件。此外,与专用集成电路(ASIC)相比,FPGA具有可重复编程的优点。

根据单位脉冲响应的不同,数字滤波器主要分为有限脉冲响应(FIR)和无限脉冲响应(IIR)2大类。在同样的设计要求下,IIR方式计算工作量较小。但难以得到线性相位响应,且系统不易稳定;FIR方式的计算工作量稍大,但在设计任意幅频特性时,能保证严格的线性相位特性;由于其实现结构主要是非递归的,FlR滤波器可以稳定工作。FIR数字滤波器是数字多普勒接收机的重要组成部分,因此,研究FIR数字滤波器的实现技术具有重要意义。随着FPGA技术的不断发展,FPGA逐渐成为信号处理的主流器件。而在FPGA中,数字滤波器不同的实现方法所消耗的FPGA资源是不同的,且对滤波器的性能影响也有较大差异。

1 FIR滤波器的原理及结构

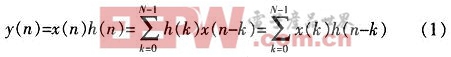

FIR滤波器存在N个抽头的h(n),N称为滤波器的阶数,其数学表达式为:

式中,x(k)为第k时刻的采样值,y(n)为滤波器输出。h(k)为FIR滤波器的第k级抽头系数。

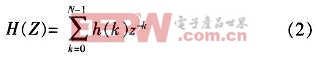

通过对h(k)进行Z变换得到FIR的传递函数H(Z),其在Z域内的形式如下:

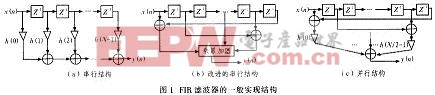

因此,根据传递函数H(Z)和FIR滤波器系数的对称性,可得FIR滤波器的一般实现结构,如图1所示。

从串行结构中可以看出,FIR滤波过程就是一个信号逐级延迟的过程,将各级延迟输出加权累加,得到滤波输出,其中最主要的运算是乘累加运算。FIR每完成一次滤波过程需要进行N次乘法和(N-1)次加法运算,N为滤波器的阶数。所以,滤波器的运算量完全取决于N的大小,当N很大时,延迟将非常长,无法实现高速信号处理。

根据FIR数字滤波器的对称特性,可以先进行加法运算,然后对加法运算的结果进行串行乘累加运算,从而得到改进的串行结构。与串行结构相比,改进的滤波器完成一次滤波的时钟周期减半,乘累加次数减半,提高了处理速度,但同时要消耗更多的硬件资源。图1(b)为Ⅳ位偶数时改进的串行结构。与串行结构相似,滤波器的运算量完全取决于N的大小,当N很大时,延迟将非常长,无法实现高速信号处理。

将串行结构展开,根据滤波器的信号流图用多个乘法器和加法器并行实现,得到FIR滤波器的并行实现结构,如图1(c)所示。并行滤波器的滤波速度快,一个时钟周期内完成一次滤波,但消耗大量的FPGA资源,如乘累加器,且器件的延迟较大,工作频率不宜太高。

FPGA具有规整的内部逻辑阵列和丰富的连线资源,特别适合用于数字信号处理。但以前FPGA一般用于系统逻辑或时序控制,很少应用在信号处理方面。其原因主要是FPGA中缺乏实现乘法运算的有效结构。随着FPGA技术的不断发展,查找表(LUT)技术的应用有效地解决了这个问题,使FPGA在数字信号处理方面得到了广泛应用。

评论