基于异步FIFO和PLL的雷达数据采集系统

3 基于FPGA实现异步FIFO设计

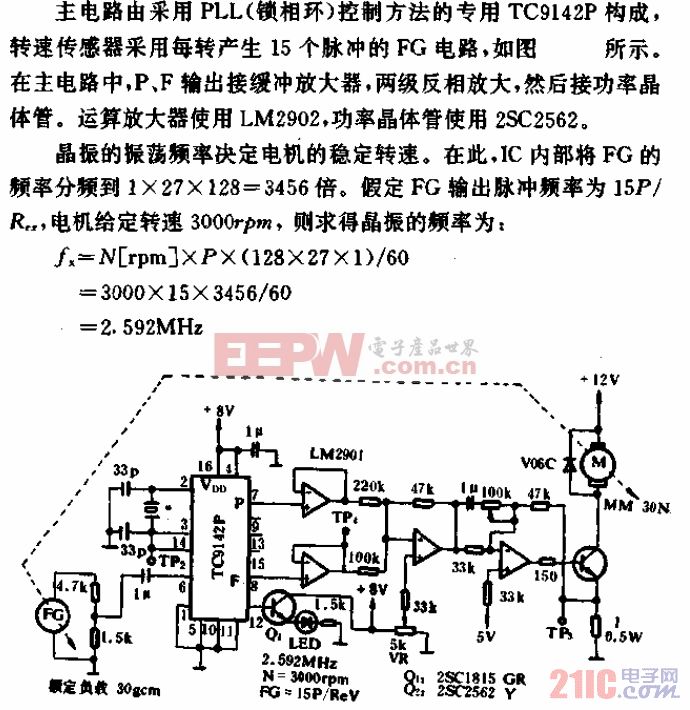

异步FIFO是在两个相互独立的时钟域下,数据在一个时钟域写入FIFO而在另一个时钟域又从该FIFO中将数据读出。异步FIFO通常被用来将数据从一个时钟域安全地传送到另一个时钟域。FIFO可作为A/D转换器件和DSP间的桥梁。使用FIFO作为输入缓冲,由A/D转换器件把采样转换的值同步写入FIFO,每写入一块数据便向DSP发出一个信号,以提醒DSP从FIFO中读取数据块。这样比单次读的效率要高的多,不会有数据丢失,且仅占用少量的系统资源。设计一个异步FIFO,读写使能由不同的时钟激励控制输入和输出数据,空/满标志既用来防止数据的上溢和下溢,也作为写入/读出控制逻辑的输入信号,用来控制A/D数据采样过程和对DSP数据的传输。当FIFO输出满标志时,写入控制逻辑停止A/D采样,等待满标志无效时恢复数据采样。从而防止数据丢失。当FIFO输出空标志时,读出控制逻辑停止DSP的数据读取,等待空标志无效时恢复数据读取。图1中FPGA内的写入/读出控制逻辑使用有限状态机设计,有限状态机能有效的进行读写时序控制,根据A/D和处理器的时序控制原理画出状态转移图,进行编程设定。

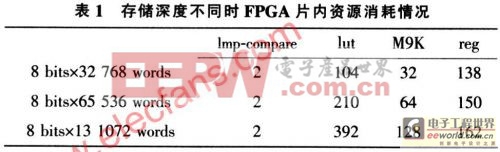

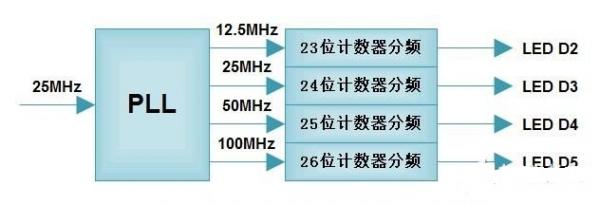

FIFO的参数指标直接影响数据采集速度。首先,FIFO的读写速度要足够快,其工作频率至少要大于等于A/D转换器件的采样率,才能充分发挥A/D转换器件的高采样率并保证无数据丢失。其次,FIFO的存储容量要适宜,容量过大会造成资源浪费,容量过小会造成溢出或数据采集速度过慢。系统FIFO采用EP3C120实现。由FPGA实现异步FIFO时,可方便的根据A/D转换器的采样精度和DSP数据宽度设计FIFO的输人数据宽度和输出数据宽度,且采用PLL设计后,可方便的调整FIFO写入端和读出端的时钟频率,使FIFO设计的高速缓存具有一定的通用性。异步FIFO是在QuartusⅡ开发环境下利用其IP核设计的,该设计的异步FIFO可支持高达256位的数据宽度;支持存储的最大深度可达131 072words,同时支持空满标志位。表1给出系统在不同存储深度时消耗FPGA片内资源的情况。可见,针对不同的数据采集需求,可利用Ahera公司提供的参数化的IP核方便的选择FIFO的数据位宽度及存储深度,避免资源浪费。

考虑到前端A/D转换速度快,精度为8位,后端DSP的处理位数一般可做到32位,为提高系统实时性,采用输入数据宽度为8位,输出宽度为32位的双时钟FIFO,如图2所示。

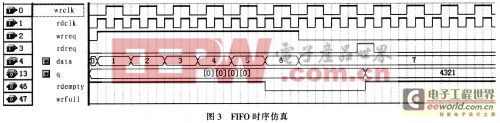

图3为对FIFO仿真的结果。双时钟FIFO输入为8位、输出为32位,且FIFO两端的读写时钟频率不同。

分析系统的吞吐率:由于A/D数据输入端口的速度固定,数据按采样频率输入FIFO,因此输入数据的时间是不变的,而DSP一次访问可取走4个有效数据,大大增加DSP读取数据的吞吐率,提高系统实时处理能力。

评论