一种基于FPGA的语音录制与回放系统的设计

0引言

随着微电子技术的发展,系统集成向高速、高集成度、低功耗发展已经成为必然,同时SoPC技术也应用而生。SoPC将软硬件集成于单个可编程逻辑器件平台,使得系统设计更加简洁灵活。SoPC综合了SoC,PLD和FPGA的优点,集成了硬核和软核CPU、OSP、存储器、外围I/O及可编程逻辑,用户可以利用SoPC平台自行设计高速、高性能的CPU和DSP处理器,使得电子系统设计进入一个崭新的模式。

该设计运用SoPC技术实现嵌入式数字化语音录制与回放。其中,介绍了在FPGA上构建WM8731的I2C总线,以及数字化语音在SRAM中的存储,并利用Matlab7.0.4软件对所采集的语音数据进行仿真。SoPC是现在电子技术、电子系统设计的汇聚点和发展方向。充分体现了其高性能、设计灵活和易用等特点。

1系统整体方案

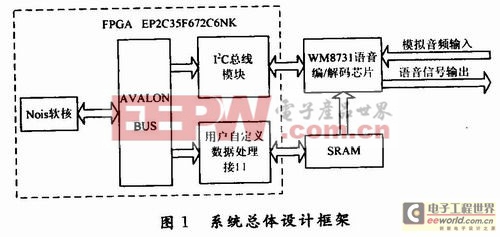

系统以Altera公司的FPGA芯片(CycloneⅡ系列)EP2C35F672C6NK为平台,结合音频编/解码芯片WM8731实现语音录制与回放。该FPGA芯片具有丰富的片内资源,大量的逻辑宏单元和多个硬件乘法器,大量的自定义I/O接口,此外还有4个锁相环,为系统提供实时时钟。设计中充分利用了FPGA的高速并行和Avalon总线自定义硬件外设的优势,从而构建了一个高集成度、高性能的系统。

语音通过话筒输入,由音频编/解码芯片WM8731以8kHz的A/D采样率转换成16位PCM码缓存。此外,为确保采集的语音数据不丢失,先将语音存储在SRAM中,再作后续处理。整体系统框架图1所示。

评论