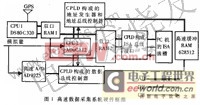

基于MAX7000系列CPLD的数据采集系统

CPLD是复杂的PLD,专指那些集成规模大于1000门以上的可编程逻辑器件。它由与阵列、或阵列、输入缓冲电路、输出宏单元组成,具有门电路集成度高、可配置为多种输入输出形式、多时钟驱动、内含ROM或FLASH(部分支持在系统编程)、可加密、低电压、低功耗以及支持混合编程技术等突出特点。而且CPLD的逻辑单元功能强大,一般的逻辑在单元内均可实现,因而其互连关系简单,电路的延时就是单元本身和集总总线的延时(通常在数纳秒至十数纳秒),并且可以预测。所以CPLD比较适合于逻辑复杂、输入变量多但对触发器的需求量相对较少的逻辑型系统。

MAX7000系列CPLD及其开发平台介绍

由于高速数据采集系统的特殊要求,在众多的CPLD器件中,选择了ALTERA公司的MAX系列器件。MAX系列的高性能和高密度是基于它先进的MAX(Multiple Array Matrix--多重阵列矩阵)架构,因此为高速应用提供了非常高的性价比。MAX7000系列还提供了业界速度最快的可编程逻辑解决方案。它基于CMOS EEPROM工艺,传播延迟最小为3.5ns,可以实现速度高于200MHz的计数器,并且为高密度的器件提供了非常宽的选择余地,十分适合高速设计时应用。该公司的MAX+plusII软件是一款易于使用的开发工具,其界面友好,集成化程度高,兼容工业标准,支持FLEXMAXACEX 1K等系列产品。并且为大学提供了学生版软件,在功能上与商业版类似,仅在可使用的芯片上受限制。由于MAX7000系列的这些优点,以下的设计都基于MAX7000系列产品。

CPLD在高速寻址中的应用

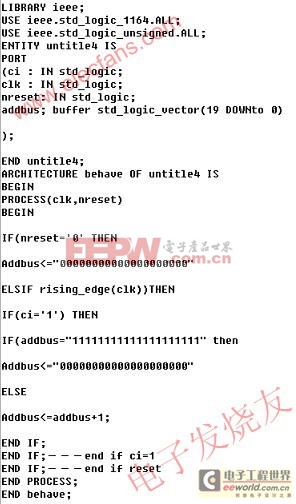

一般的数据采集均需由CPU将A/D转换的结果读入,然后再转存到片外的存储器中,这样至少需要4个机器周期。如果按照一般一个机器周期为1μs,那么最高采样率只能达到250kHz,绝难满足高速采样的需要。在本系统中,直接将采样数据存到高速缓冲RAM中,而存储器寻址则采用ALTERA公司的EPM7032LC44-6构成的地址发生器来完成。写信号可采用A/D转换的时钟信号,但需经过一系列分频及逻辑组合,也可另由电路产生或放在地址发生器中。EPM7032LC44-6构成地址发生器的基本原理是采用5片级联的74161组成20位的同步计数器,第20位接在高速缓冲RAM的片选线上,用来切换缓冲存储器组。用CPU2的P1.7控制计数允许端,异步清零,则20位地址线输出保持同步。其具体的实现可以采用图形编辑输入或者文本编辑输入的方法。下面给出其VHDL语言程序。

其仿真结果如图2所示。

评论