高清液晶电视LCD屏检测仪的设计

随着多媒体技术的快速发展与普及,液晶显示屏(LCD)在生活中的使用十分普遍。因为目前高清电视的分辨率大多不为电脑显卡所支持,传统的电脑软件测试方法无法满足个体用户对显示屏质量的测试需求。为解决此问题,本文设计了一款价格低、使用灵活、体积小巧的便携式多分辨率LCD图样发生器,可以为实验室人员和消费者提供逐点检测高清液晶屏的机会。

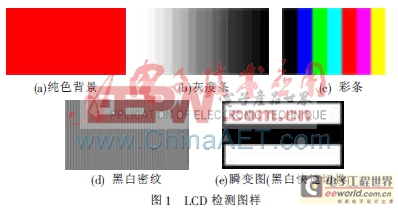

1 LCD检测项目及样图

1.1 检测项目

(1)坏点检测

坏点主要有亮点、暗点两种。质量上乘的液晶显示器要求在全黑图样下无亮点,在全白图样下各点亮度均匀,暗点数目小于3个而且不能出现相邻坏点。本产品坏点检测图样为纯色背景。

(2)对比度

对比度就是把白色信号在100%和0%的饱和度相减,再除以用光照度Lux(即勒克斯,每平方米的流明值)为计量单位下0%的白色值所得到的数值[1](0%的白色信号实际上就是黑色)。较高的对比度对应着显示图像的高锐度,能带来更丰富的色彩层次感。本产品对比对检测图样为灰度条。

(3)色彩

丰富、逼真的色彩显示是LCD的一大特色,而色彩的显示准确程度也是屏幕质量的衡量标准之一。本产品选用彩条图样来检测。

(4)分辨率

高分辨率的屏幕能显示更加精细的画面。但是屏幕实际的显示能力还要接受仪器的检验。本产品用黑白密纹图样来检测屏幕的水平分辨率和垂直分辨率是否真实,并检测色偏现象的发生。

(5)响应速度

响应时间决定了显示器每秒所能显示的画面帧数,更快的响应速度是为更优质的连续画面显示提供硬件的基础。本产品将用瞬变图和移动方块图样来定性检测屏幕响应速度。

1.2 检测样图

检测样图如图1所示。

2 系统设计

本文使用Altera公司型号为EP3C16F484C6的FPGA芯片和DE0开发平台。设计的环节包括软件设计、设计综合、仿真验证、下载验证。采用的软件工具为QuartusⅡ9.1,描述语言为VerilogHDL。本设计支持三种常用的显示分辨率:各类液晶显示器通用的640×480@60 Hz、4:3屏幕的高分辨率模式1 280×1 024@60 Hz、16:9高清模式1 920×1 080@60 Hz。每种分辨率下,都支持七种检测图样的VGA显示。在产品外形的设计上,以简洁、实用为基本要求,旨在节约成本的同时提供给用户便捷的操作体验。

2.1 系统结构与外形设计

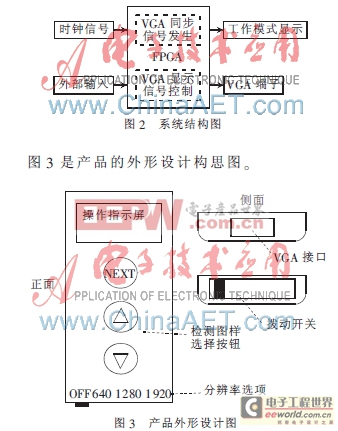

图2是LCD屏检测仪的系统结构图,系统功能主要由核心器件FPGA实现。

2.2 系统模块

从图2可以看到,本系统主要包括时钟信号发生模块、VGA同步信号产生模块、VGA显示控制模块、外部输入处理模块和工作模式显示模块。时钟发生模块用于产生不同分辨率下扫描所需的像素时钟;VGA同步信号产生模块用于产生输出的行同步、帧同步信号;VGA显示控制模块根据外部的输入来控制VGA显示数据的输出,从而产生特定的检测图样;接口方面的外部输入处理模块则负责按键的消抖和显示模式的译码工作。工作模式显示模块用于向用户指示产品当前的工作状态。

3 系统功能实现

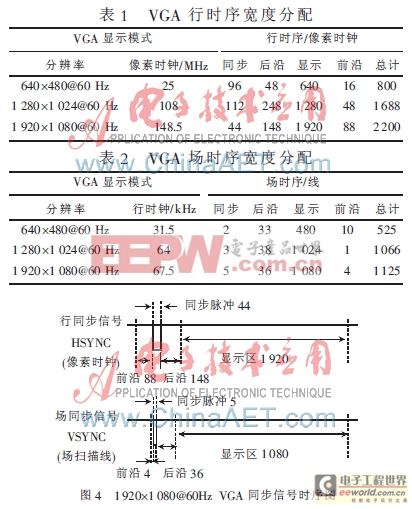

3.1 VGA时序说明

本系统需要由VGA输出的信号包括:行同步信号(HSYNC)、场(帧)同步信号(VSYNC)、RGB数据信号(模拟值)。其中至关重要的是行、场同步信号,只有正确地输出与分辨率相应的同步信号,才能准确、稳定地在LCD上显示检测图样。根据VGA视频传输标准,屏幕着色从左上角开始,从左到右、从上到下逐行扫描,每行扫描结束后都要由行同步信号实现显示器的行同步,每一帧的扫描结束后都要由场同步信号实现场同步。视频电子标准协会(VESA)对显示器时序做了规范,行时序和场时序都要包括同步脉冲(Sync)、显示后沿(Back Porch)、显示区(Display Interval)和显示前沿(Front Porch)四个部分。VGA工业标准还规定了同步信号的负极性,即同步脉冲信号为低电平[2]。

表1、表2分别是VGA行、场时序宽度分配[3],图4是同步信号时序示意图。

特别需要注意的是,行同步信号各阶段持续时长的单位是像素时钟周期,而场同步信号各阶段持续时长的单位为行时钟周期(线),即扫描一行的时间长度。

3.2 像素时钟的产生

由于高分辨率模式所需的像素时钟往往都大于100 MHz,不能由开发板自带的晶振分频产生,所以在设计中采用了Quartus中Tool->MegaWizard Plug-In Manager产生 IP核中的ALTPLL模块,实现数字锁相环PLL,将50 MHz的原始时钟信号转变为稳定的高频像素时钟。

3.3 VGA行场同步信号发生

下面是本设计中VGA同步信号产生的VerilogHDL描述:

reg [11:0] h_cnt, v_cnt;

always @(posedge clk_pix or negedge rst_n)

if(!rst_n)

h_cnt = 0;

else if(h_cnt == H_TOTAL)

//scanning of one line finished

h_cnt = 0;

else

h_cnt = h_cnt + 1'b1;

always @(posedge clk_pix or negedge rst_n)

if(!rst_n)

v_cnt = 0;

else if(h_cnt == H_TOTAL)

if(v_cnt == V_TOTAL)

//scanning of one frame finished

v_cnt = 0;

else

v_cnt = v_cnt + 1'b1;

assign VGA_VS=(v_cnt>=0 v_cntV_SYNC)?1'b0: 1'b1;

assign VGA_HS=(h_cnt>=0 h_cntH_SYNC)?1'b0:1'b1;

3.4 检测样图信号的产生

由于检测图样多为有规律的色块,在图样产生过程中可以充分利用位运算来提高信号产生的速度,减少对存储单元的依赖。

3.5 仿真结果

本设计采用ModelSim专业仿真软件进行仿真。对于PLL模块,由于SE版本的ModelSim不支持Quartus II内置IP核,可以在Quartus II内独立仿真;对于其他模块,建立testbench.v测试文件,在ModelSim中新建项目进行编译、仿真。图5、图6分别是 PLL模块与VGA同步信号发生仿真结果。

仿真图中,clk是晶振产生的50 MHz时钟;rst_n是低电平有效清零输入;VGA_HS、VGA_VS分别为行同步、场同步信号;ready_sig为有效显示区指示信号;frame_sig为帧脉冲,每帧结束时产生一个高脉冲;x_addr、y_addr为当前扫描像素的坐标。

4 实际测试效果

产品的所有功能在Altera公司提供的DE0开发板上实现。图7是在SHARP 46英寸液晶屏(分辨率为1 920×1 080@60 Hz)上的实测结果(照片)。

由于VGA有着较为广泛的使用,所以本设计的图样输出接口设计成VGA模拟信号的输出。随着存储设备容量的扩大和信息传输速度的加快,未来的高清视频和高清图像的显示将由数字传输取代模拟传输。所以,若要进一步改进本文高分辨率LCD屏检测仪的设计,可以考虑增加HDMI和YPbPr多端子的输出,并进一步扩大检测分辨率范围,从而保证检测仪能适应更多LCD屏的检测。

参考文献

[1] 田佳天.高清SDI电视测试信号源在FPGA硬件平台上的设计和实现[DB/OL].http://www.paper.edu.cn,2010-12-23.

[2] 王恒心,熊庆国,王鑫,等.基于FPGA/CPLD的嵌入式VGA显示系统[J].微计算机原理,2008:146-148.

[3] VGA信号时序关系(VGA Signal Timing)[DB/OL].http://tinyvga.com/vga-timing.2011-02.

评论