LED显示屏数据处理技术介绍

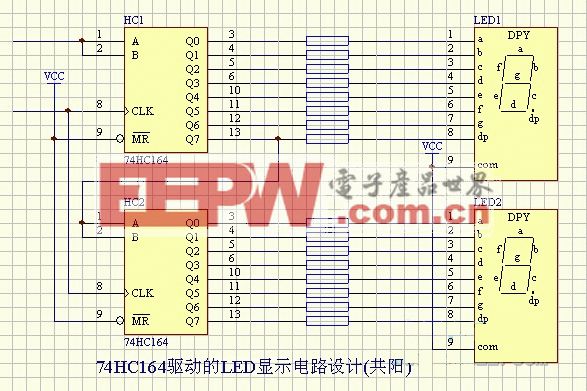

LED数据处理设计中,数据的存储有两种组织方式(图1):①组合像素法(Packed Pixel Method):即画面上每个像素的所有位均集中存放在单个存储体中;②位平面法(Bit Plane Method):即像素的每一位各自存放在不同的存储体中。由于使用了多个存储体,它们可以一次同时读出更多的像素信息。从两种存储结构来分析,利用位平面结构有利于提高LED屏的显示效果。

本文引用地址:http://www.amcfsurvey.com/article/221999.htm

图1 数据存储的两种方式

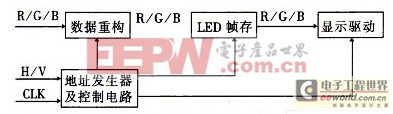

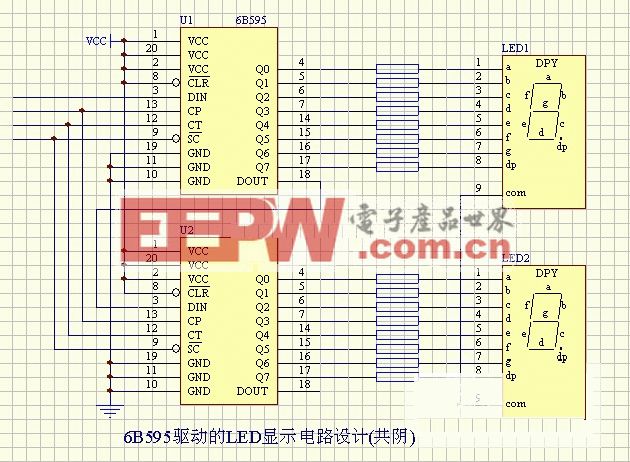

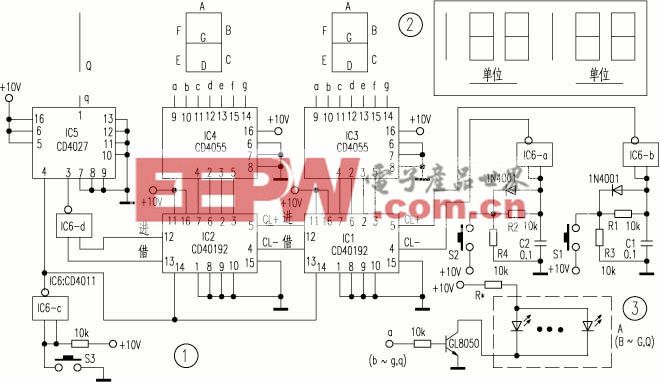

整个LED显示屏显示控制电路结构框图如图2所示。其中,数据重构电路完成RGB数据的转换,将不同像素的同权位组合在一起,然后存放在相邻的单元中,从而以位的形式完成整个数据的重新组合。

图2 显示控制电路

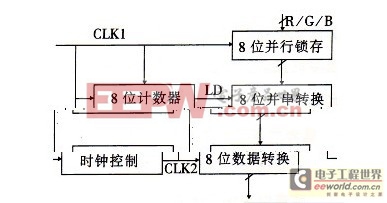

数据重构电路主要由四大部分组成:8位数据并行传送电路;8位并-串转换电路;8位数据锁存电路;8位加1计数器。R/G/B各8位数据由经同步处理后的像素点频打入并行锁存器,8位加1计数器输出进位脉冲LD,将8位数据同时锁存到8位并-串转换电路,由时钟控制电路完成并-串转换电路时钟的控制。数据经过重构后,一个存储体中不再是一个像素值,而是不同像素值的同权位。将所有的同权位存放在一起,从而构成以位为单位的位平面存储结构。在读出时必须按相反的规则取出各像素的相邻权值。

图3 数据重构电路

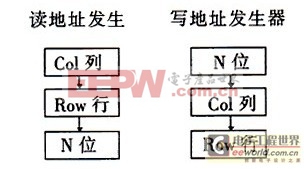

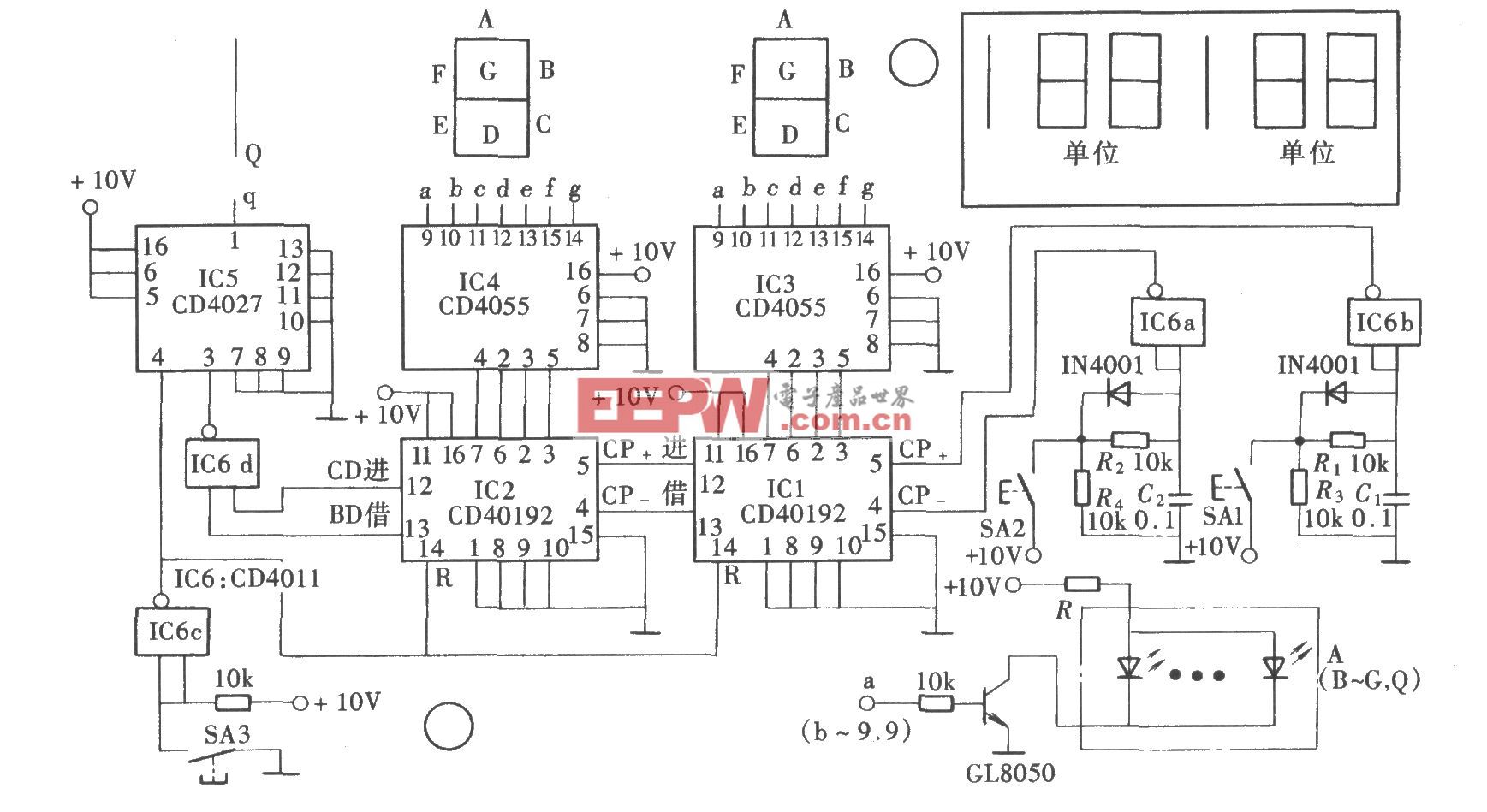

读写地址发生器必须满足严格的时序。对同一存储芯片来说,可将其分为N片(一个像素值用N位表示),每片表示一个位平面,像素经过转换向同一存储器写入时,首先写0位,再写1位,最后写N位。对于8Col×Row点阵的显示屏,每个位平面存有8Col×Row位。存储器内部组织取决于驱动屏体上像素管的逻辑连线关系。根据存储器组织,读地址发生器由列驱动行,再由行驱动位;写地址发生器则采用由位驱动列、列驱动行的方式,从而可以保证读写同步性,正确地同步显示原始图像信。

图4 地址发生器

评论