基于ARM内核SoC的FPGA 验证环境设计方法

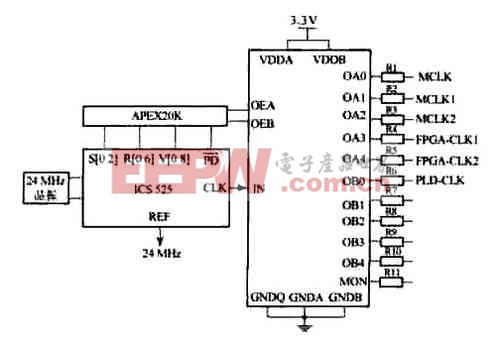

图3 时钟电路

时钟频率f CLK用下式调节:

式中:f i 为输入频率;v 为4~511 中的自然数;r 为0~127 中的自然数;OD 值由S[0 ,1 ,2 ]的3 位决定,S2S1S0的组合为:000 对应十进制10 ,001 对应2 ,010 对应8 ,011 对应4 ,100 对应5 ,101 对应7 ,110 对应9 ,111 对应6。注意:时钟电路的频率调节最终通过驱动软件进行各个参数的配置,在FPGA 内应有相应的配置寄存器,同样,下面的复位控制模块也应有复位配置。

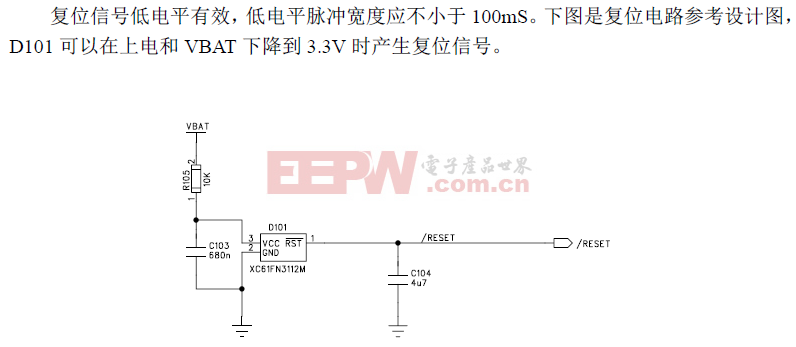

复位电路的设计

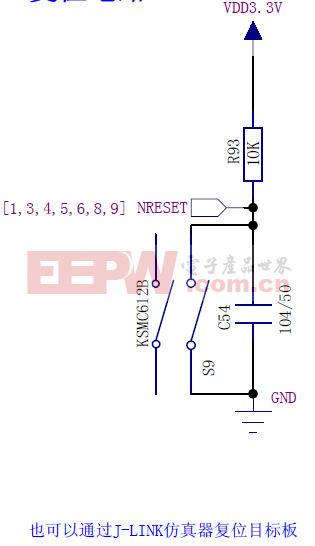

复位信号包括接口模块中的外部硬件按键复位信号reset 、上电复位信号power on reset 、联合测试访问专家组(JTAG) 复位信号nTRST 和软件调试复位信号nSRST。以上几个信号都是必须的常用复位信号,但ARM7TDMI 核只提供了两个复位信号接口reset 和nTRST ,为此,以上4 个信号必须加入适当的逻辑电路使其最终形成2 个复位信号,复位信号通路必须满足复位时序要求且与时钟信号通路一样越短越好。

评论