基于ARM内核SoC的FPGA 验证环境设计方法

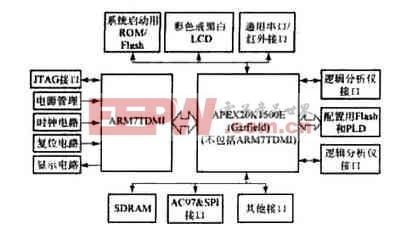

图2 中外围电路的主要功能是验证SoC 中各个接口IP 模块能否与ARM7TDMI 核、外部接口单元、硬件驱动软件和实时操作系统协调高效地工作。由于接口(如USB 接口、UART/ IrDA 接口、SPI 和LCD 接口等) 电路结构比较简单,且很多资料都有介绍,在设计时,除了注意通用的设计规则和印制电路板(PCB) 布局布线外,没有特别的要求(总结构框图中所有外围电路都在该开发验证系统中调试成功) ,同时,为了便于分析各个被验证的IP 模块在任意时刻的状态, 我们将APEX20K1500E 的大多数I/ O 引脚都引出到PCB 上,以方便SoC 开发人员使用逻辑分析仪进行信号实时采集和分析,也可让信号发生器产生一些特定信号通过以供系统调试使用。该开发系统在PCB 的设计时还特别注意了电磁干扰的屏蔽。

图2 验证平台结构框图

电路设计

电源的设计

拥有符合FPGA 要求的电压对该验证环境的设计十分重要。根据SoC 的发展趋势和APEX20K1500E增强型I/ O的特点,该平台选用2 . 5V内核电压和3. 3 V 的I/ O 电压,同时提供2. 5 V 和1. 8 V 可选电压,以满足SoC 更低电压、更低功耗的发展要求,方便以后重复使用。

时钟信号电路的设计时钟电路如图3 所示。

ARM7TDMI 核有2 个时钟:存储器时钟MCLK 和内部TCK产生的时钟DCLK。在正常操作期间,内核由MCLK 供给时钟, 内部逻辑保持DCLK 为低。当ARM7TDMI 核处于调试状态(nWAIT 必须为高) 时,内核在TAP 状态机控制下由DCLK供给时钟,且MCLK可以自由运行。所选时钟在信号ECLK上输出,以便外部系统使用。在监控模式下,内核由MCLK供给时钟,且不使用DCLK。所以,首先应供给存储器时钟MCLK。由于该系统除了拥有ARM7TDMI 核外,还包括电源管理模块、复位管理模块、状态和控制寄存器等,应当额外供给时钟MCLK1 和MCLK2。用以验证可复用IP 的芯片APEX20K,也需要提供至少2 个时钟(FP2GA2CLK1 和FPGA2CLK2);用做配置芯片的PLD 也需要提供一个时钟(PLD2CLK) ;各个FPGA 和整个FPGA电路设计都采用全局时钟控制方式,所有的时钟都是由ICS525201 芯片产生,该芯片是一种可调时钟芯片。

评论