低功率时钟选项——满足客户的低功率需求

不断增长的低功率电子设备需求在消费、工业和汽车市场的各个角落随处可见,无论应用是由市电供电还是电池供电。不断上涨的能源成本、更高的竞争基准要求和日益严格的立法控制只是对最新一代电子产品提出更高功效要求的几个要素。

通过深入到最新的微控制器(MCU)的核心,就有可能从根本上实现低功耗。本文一开始先介绍了飞思卡尔MC9S08系列产品提供的几种不同时钟模块,然后详细介绍了多功能时钟发生器(MCG)提供不同时钟选项。这种发生器是当今系列产品中最灵活的模块。本文向读者介绍时钟选择对于在应用中实现低功率运行是多么重要。

本文介绍了MCG的工作原理,并详细介绍了帮助降低功耗的一些属性,如锁相环(PLL)、锁频环(FLL)、分频系数,最后讨论了这些属性如何影响时钟的精确性。

时钟考虑

时钟负责在整个CPU和其他MCU外围设备中提供基本定时和同步信号。时钟信号由外部源(如水晶)或内部源(如RC电路)提供。应用将最终确定采用哪一种时钟源,因为每一种时钟源都有自己的优势。

从根本上讲,MCU的时钟速度越快,该设备的功耗越高,反之亦然。为了延长电池供电设备的寿命或者设计更小巧、更简单的电源(针对市电供电应用),降低微控制器的功耗非常重要。时钟只是微控制器中影响功耗的众多特性之一。

飞思卡尔的多功能时钟发生器

在飞思卡尔的8位MC9S08系列产品中,您可以采用内部时钟源(ICS)、内部时钟发生器(ICG)或多功能时钟发生器(MCG),具体取决于用户选择哪种MCU。在采用飞思卡尔设备的各种应用中,有3种模块可以用来支持这些应用。每一种时钟模块都具有相似的属性,ICS可以被看作是ICG的一个子集,MCG可以被看作是ICS和ICG的合并。MCG在设计时充分考虑了高端应用的需求,而ICS则恰恰相反,它适合体积较小、对成本敏感的MC9S08设备。尽管MCG可提供最广泛的功能,但有时结合使用ICS和ICG可能并不合适,因为某些应用可能只需要ICS和ICG分别提供的功能。表格1对这3种时钟模块进行了简单对比。

1 带有ICS的模块可能不包含振荡器,因为它们可能没有足够数量的针脚。在没有外部时钟源的情况下,模块只有3种运行模式。

2 这些不包括“关闭”模式。

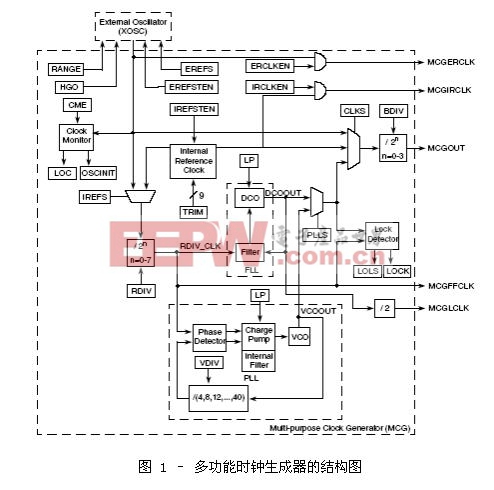

由于功能的增加,MCG是3种模块中功能最多的模块。PLL、FLL、内部或外部生成的参考时钟可以为用户提供多种选择。图1显示了MCG的结构图。

PLL电路可以为设计人员提供精度最高的时钟解决方案。它采用了外部振荡器,但内部参考时钟可以最大限度地节约功率。因此我们可以采用8种不同模式运行该模块。用户可以在他们的应用中随时在这些模式之间切换:

·FLL Engaged Internal(FEI)

·FLL Engaged External(FEE)

·FLL Bypassed Internal(FBI)

·FLL Bypassed External(FBE)

·PLL Engaged External(PEE)

·PLL Bypassed External(PBE)

·Bypassed Low Power Internal(BLPI)

·Bypassed low Power External(BLPE)

每一种运行模式的全部细节不在本文讨论范围之内,但有关MCG 运行模式的信息可以从飞思卡尔技术培训中心(http://www.freescale.com/training)提供的MC9S08 MCG在线培训资料中获取。根据MCG支持的应用的不同,上述每一种模式都具有它们独特的优势。

不同运行模式的功耗互不相同。我们可以这样说,采用内部组件的模式所消耗的功率少于采用外部组件的模式。而MCG包括两种专门为低功率应用设计的模式——旁通低功耗内部(BLPI)和旁通低功耗外部(BLPE)。驱动BLPI模式的总线频率要比BLPE 模式低,因此BLPI 模式消耗的功率最小。图2总结了每一种运行模式的功耗。

旁通低功耗运行模式

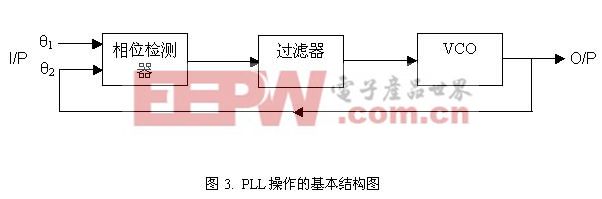

在这些模式中,FLL或PLL被旁通,系统时钟源从内部时钟(BLPI)或外部参考时钟(BLPE)中获得。要了解涉及旁通锁环电路的低功耗运行模式,我们应注意PLL/FLL的运行方式。PLL有输入时钟信号必须经过的几个阶段,如图3所示。

PLL的目的是不断对比输入信号的相位和输出信号的相位并调节出现的任何差异,从而保持频率信号。一般而言,PLL包括一个相位检测器、低通过滤器和电压控制振荡器(VCO)。相位检测器对两种输入值的相位进行对比并提供与相位差异成比例的输出,然后这些输出通过低通过滤器过滤。VCO负责将频率输出转换成相位输出,最后一个阶段提供输入反馈(负的),以便重新开始整个过程。很明显,保持非常精确的时钟源的过程可能需要大量功率。FLL的运行方式稍有不同,它可以锁定频率而不是相位。因此旁通PLL(或FLL)阶段并使用外部/内部时钟源消耗的功率更低,但代价是整体时钟精确性的下降。直接时钟源的精确性由水晶(外部源)或RC电路(内部源)的质量决定。

这些低功耗旁通模式可以进一步降低功耗,因为它们运行时不需要启动后台调试通信(BDC)设备。这意味着这些运行模式下不能进行调试。然而,如果需要BDC,该模块会自动切换到可处理BDC的适当旁通运行模式(即FBE、FBI或PBE)。

由于 PLL/FLL没有运行,导致两种模式出现固定频率范围。在BLPI模式中,内部参考生成器 固定为31.25kHz-39.06kHz,因此总体功耗最低。另一方面,BLPE模式的频率范围非常大(低范围:32kHz-38.4kHz;高范围:1MHz–16MHz),因为PLL/FLL不会对外部参考频率设定任何限制。在MCG控制寄存器2中,用户还可以选择总线分配器(BDIV)位功能,使时钟源可以除以1、2、4或8系数——注意,更低的总线时钟速度可进一步降低功耗 。

MCG控制寄存器 2还包含其他基本位,使模块可以以低功耗运行。低功耗选择(LP)位控制在旁通模式下是否禁用PLL(FLL)。这种具体操作已在前面讨论过。该寄存器还包含一个高增益振荡器(HGO)选择位,可以控制外部振荡器。用户定义设备是否应当以高增益还是低功耗运行。为了最大限度地降低功耗,低功耗模式将限制振荡器针脚上的电压摆动,而高增益运行会带动振荡器针脚上的轨至轨(rail-to-rail)电压摆动。

MCG寄存器的其他功能包括MCG状态、控制寄存器锁丢失和时钟监控器位丢失。如果发生锁/时钟丢失事件,这些功能会触发中断/复位操作。关闭这些功能可以进一步降低功耗,但也会降低系统的强韧性。

结论

MC9S08DZ系列产品中目前提供的MCG模块能够为应用设计人员提供多种运行模式。这些模式都具有不同属性,适合各种应用。PEE模式可通过采用外部源(尽管是PLL)提供最高的时钟准确率,但代价是功耗最高。相反,BLPI模式下时钟速度最慢,消耗的功率也最低。显然,性能提高,功耗也会相应增加。

还有一些措施可以进一步降低功耗,如关闭时钟丢失和锁丢失功能及利用总线频率分配器功能。后一种属性可用于任何运行模式,可以帮助降低功率而不需要利用旁通模式。

评论