构建高性能的同步锁相系统改善广播视频定时

一个新的信号进入到演播室,首先需要做的事情就是通过使用同步锁相电路将其与演播室中的其他信号同步。同步锁相系统由均衡器、解串行化器、同步分离器、串行化器、帧传冲器以及定时控制六个功能模块组成。本文将分析从这六个模块来改善视频系统定时性能的方法。

稍微注意一下就可以发现,在世界上有很多种不同的广播视频演播室工作在不同的格式,一些是数字信号,一些是模拟格式的信号。今天,美国在使用的就有多种高清电视光栅格式。如果你试图计算SMPTE292M HD标准涵盖的不同光栅格式的数量,恐怕有数十个之多。

在任何演播室内都有很多不同的信号,它们之间相互同步。用视频术语的说法就是它们是同步锁相的。同步锁相允许在一个信号和另外一个信号之间简单地切换,不需要中断接收设备中的同步电路。为实现这点,需要将任何外部源信号同步锁相到演播室中的其他信号。大多数演播室使用模拟信号作为他们的定时基准信号,定时信息需要从这个信号中截取,以允许用于对输入信号进行同步锁相。

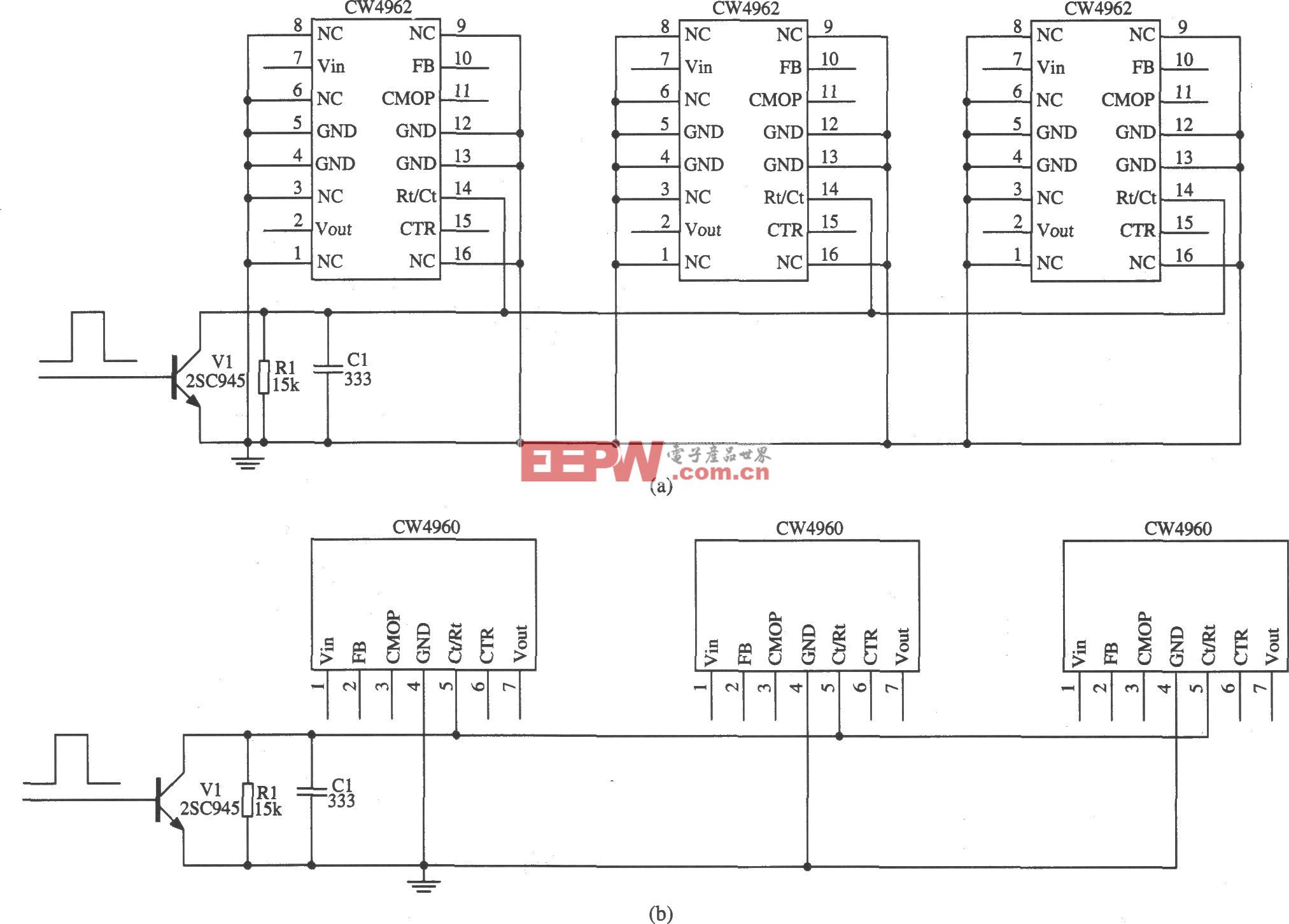

当一个新的信号进入到演播室,无论这个信号是来自卫星电视接收器、摄像机或者任何其它来源,首先需要做的事情就是通过使用同步锁相电路将其与演播室中的其他信号同步。图1所示为同步锁相系统的功能框图,在这个框图中获得一个SDI(串行数字接口)输入信号,并将其与一个提供的模拟基准信号同步。在本文中,我们将详细地了解这种应用,以及这六个模块的设计考量。

图1

电缆均衡器

在视频广播设备上的SDI输入通常支持很长的电缆传输:对于高清晰度视频信号可以达到140米以上,对于标准清晰度信号可以超过300米。为支持更长的电缆,需要增加电缆均衡器。

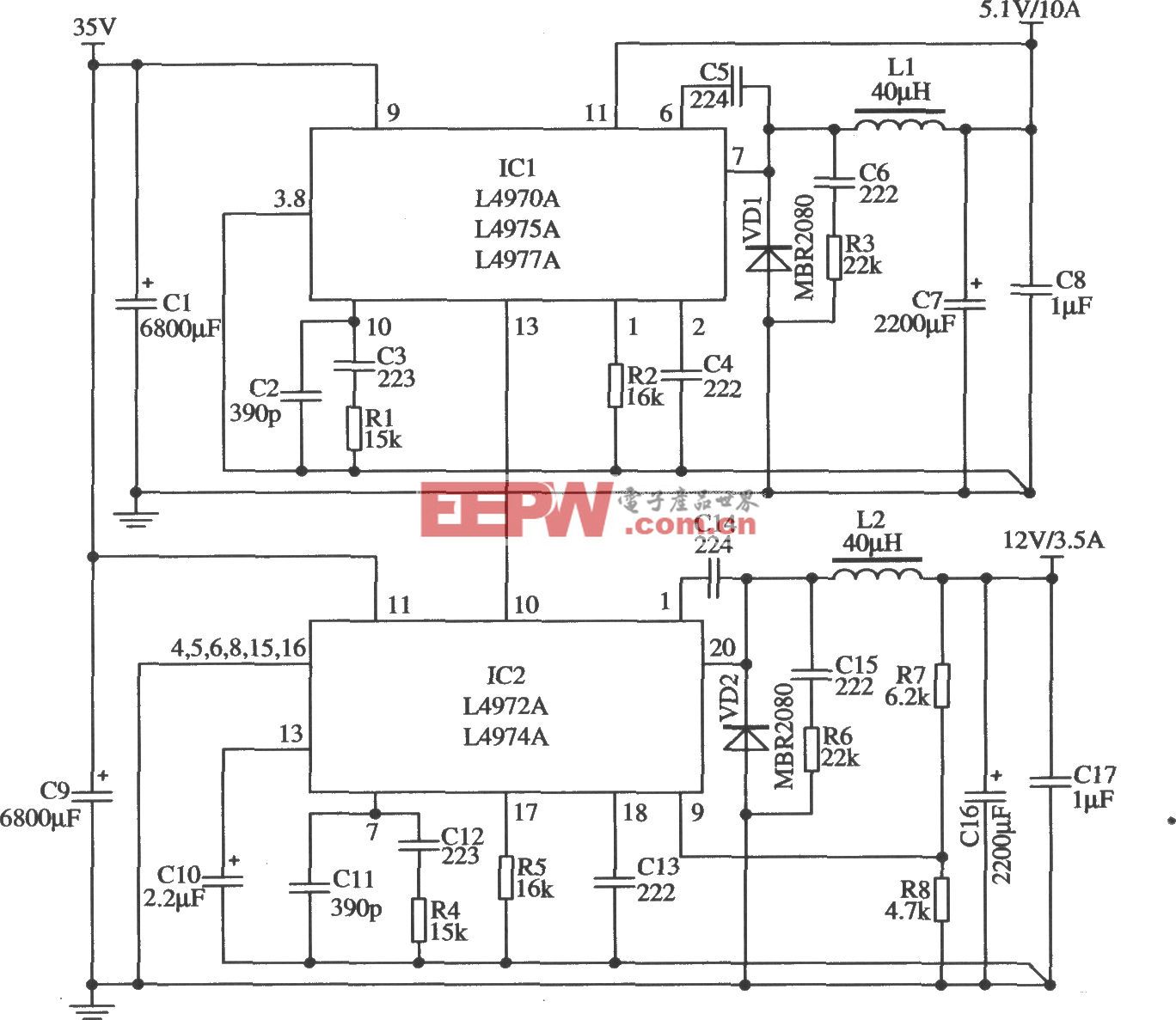

长的电缆具有低通的特性,在这个电缆中输入信号的衰减与电缆的长度成正比,以及与频率的平方根成正比。图2显示了一个长100米的普通电缆(Belden 1694A)的频率响应。

图2

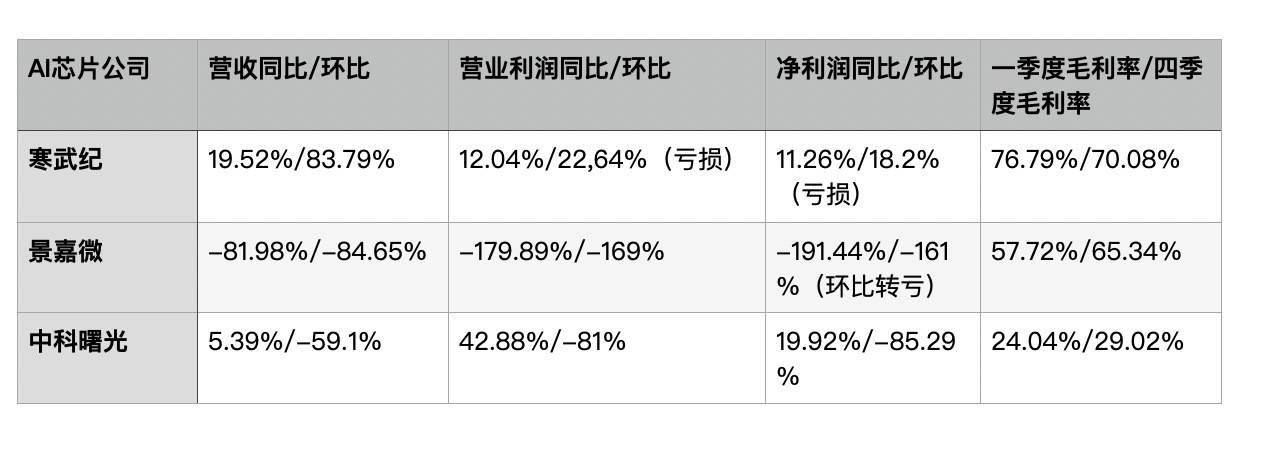

尽管了解到随频率改变衰减的变化对于设计用于恢复信号的滤波器很有用,但是你真正想看到的是眼图。眼图能告诉直观地让你从信号眼图的张开程度判断是不是足以能恢复数据。图3显示了1.5Gbps信号(HD-SDI信号)通过多种不同长度电缆后的眼图,随着电缆的长度增加,眼图的张开度出现非常明显的变化。就本文的观点来说,趋肤效应的主要结果是随着频率的增加,电缆中用于承载信号的导体横断面部分越来越小,因此越高频率的信号衰减越高。这种损耗的响应曲线将正比于,这使得对于标准类型的滤波器来说,进行补偿更加困难。

图3

为匹配电缆的频率响应,设计师必须很小心地在他/她的滤波器中配置零点,以使最终的响应更接近电缆的响应。

为满足同时要求高增益和高带宽的需求,在外部实现均衡器电路,采用像美国国家半导体公司的0.25微米BiCMOS SiGe工艺。这些均衡器的一种实例如LMH0044电缆均衡器,该器件具有从143 Mbps到1.485 Gbps的很宽数据速率范围,可以实现直流恢复以正确处理失真数据条件(对于低数据速率的应用,直流恢复可以被旁路),该均衡器可以以单端终结或差分配置进行驱动。它具有的其他功能包括分离的载波检测和输出静噪(mute)管脚,当没有信号时将两个管脚连接,使输出处于静噪状态。采用该器件,你可以在200米的Belden 1694A电缆上恢复高达1.5Gbps的数据率信号。

解串行器

在你完成使输入信号的“眼图”展开的艰难工作之后,你必须使输入的数据位有意义,这个工作需要使用到解串行化器。视频图像具有一个非常有规则的重复格式,它们是独立的数据位组成,这些数据位在下一个最高级组织中被划分成10位的字,然后依次划分成像素。一串像素组成一条线,一系列的线又组成一个场,一个或更多的场组成一个完整的视频帧。

为整理出这个组织,SMPTE数据在每一条线的起始与结束时发送一个称为定时基准信号(TRS)的特殊序列。通过检测这个TRS,它允许接收器计算出每个信号的字和线的排列。在每条线的末尾插入一些额外的字,这些字用于告诉接收器这条线的序号。同时还包括了CRC,这样接收器就能判断它是否正确地接收到这条线中的所有数据。

下面几种情况会对收器的正确接收造成很大影响:直流内容和长段时间内没有转换(0与1之间的转换)。大多数通信系统具有控制这个问题的方法,就SMPTE 292串行标准(HD-SDI)而言,它同时对数据采用了扰码和编码处理。

一个好的解串行化器将能截取所有这些信息,为你提供你的系统所需要的信息。对于本应用来说,它由图像数据和定时数据组成。像LMH0031这样的解串行化器将能实现这样的工作,在10位的数据总线上输出图像数据。定时数据以三种数字信号的形式呈现,分别代表H(水平线开始)、V(场间隙起始)和F(帧起始)。如果光栅格式不是隔行的,则你可以只使用H和V,因为它们是相同的。

串行数据进入到解串行化器,在这里这些数据被解码并被解扰。然后进行分析以发现TRS,TRS可以让解串行化器知道如何将这些位数据分成字。进一步对TRS进行分析来获得被编码的定时信息,对定时信息进行解码并解扰数据,然后确定组帧,这样解串行化数据可以正确地进行字排列。所有这些活动通常都在解串行化器中完成。

分离器与PLL的同步

尽管视频领域大多数时候都是数字的,但其中有个领域依然常见为模拟的,那就是同步基准信号,演播室用这个信号来同步所有的设备。最常用的基准信号是一种不包含图像信息的视频信号。这是由一串脉冲信号组成,用于标志每个视频线的起始,一种特定的模式用于标志每个场或帧的结束。在我们的同步锁相电路的这个模块中,一个同步分离电路从基准信号中获取H、V和F(水平线起始、场起始和新帧的起始),PLL电路产生一个像素时钟,该时钟与基准信号同步。

标准模拟标清或高清视频信号,输出以CMOS逻辑电平提供所有的关键定时信号,包括复合同步信号、水平同步信号和场同步信号。其水平同步信号输出具有低抖动的特点,不需要采用外部电路来消除抖动。LMH1981能自动地检测输入视频格式,因而不需要采用微控制器或外部RSET电阻进行编程设定,并应用50%的同步限幅以确保准确的同步提取,即使是输入具有不规律的幅度、偏移或噪声条件。

为产生像素时钟,PLL应该设置以锁定到LMH1981的行同步信号(Hsync)输出,并产生期望的时钟频率,对于标清视频信号来说这个频率为27MHz,对于高清视频信号来说为74MHz。当使用PLL来产生时钟时需要考虑的事情是分频比可以非常大并减少环路带宽,这可能使得PLL对行同步信号上的抖动非常敏感。因此,选择一个具有非常低抖动行同步输出的同步分离器非常重要。

帧缓冲器

帧缓冲器是一个简单的存储器模块,具有足够大的容量来至少保存一个完整的图像帧。这个缓冲器需要有两个端口,这样一来,从解串行化器中来的数据可以被写入到缓冲器的一端,同时数据可以从缓冲器的另一端独处,以馈入到串行化器中。缓冲器的组织与视频图像一样,连续的像素组成完整的线,连续的线组成一个完整的帧。

定时控制

定时控制是整个同步锁相系统的核心,定时控制的基本功能是对帧缓冲器写入以及从帧缓冲器中读取的控制。定时控制需要跟踪两个不同的定时域。在输入端,它接收来自解串行化器的数据、定时信息和时钟,数据被写入到帧缓冲器中,利用一连串的计数器来跟踪像素和线信息。这个数据的写入与从解串行化器中恢复的时钟同步。同时,定时控制从同步分离器和像素时钟中获得定时信息。

这些与第二组计时器一起用来从帧缓冲器器中读取数据。这个数据与基准同步信号同步读出,这样一来,解串行化器接收到的图像就可以与基准信号同步读取。

数据随同像素时钟一起被馈入到串行化器中以输出。尽管视频信号具有非常严格的定时规范,在输入和输出数据速率之间存在一些差异,这种差异意味着最终帧缓冲器将要么腾空,或者要么溢出。定时控制电路必须识别出这种情况,并周期性地重复一个帧,或者丢弃一个帧以保持输入和输出之间的定时差异小于帧缓冲器的大小。

串行化器

一旦数据从帧缓冲器中读出,这些数据将是并行的格式。在它被发送到下一个设备之前需要进行串行化和格式化以满足SMPTE 292M HD-SDI标准。从数字的角度来看,将产生和插入新的TRS参数,计算并插入新的行号以及CRC,数据通过SMPTE扰码算法进行扰码处理,并在从并行数据转换到串行移位寄存器之前转换成NRZI格式。

正确实现这些的关键是使用一个足够干净的时钟,以满足严格的视频定时规范以将数据移出。SMPTE 292M允许在串行化输出上不超过0.2UI的抖动峰峰值,这意味着时钟抖动应该低于大约100 ps p-p。大多数串行化器采用并行数据速率的时钟作为它们的输入时钟(对于高清,这个时钟接近74MHz),然后进行倍频以达到1.5GHz的串行速率。

大多数好的串行化器都会使用PLL用于这种倍频,这样可以抑制掉最初的并行时钟上的抖动。然而,为获得最佳的性能,最好采用干净的时钟。在示例的同步分离器/时钟发生电路中,将采用一个具有非常低抖动的VCXO来产生像素时钟,这样加上串行化器非常低的抖动抑制特性,将可以获得非常低的抖动输出。采用LMH0030串行化器以及VCXO时钟源,你可以得到的串行抖动接近75ps,远远低于0.2UI。

评论