P87LPC764利用I2C总线扩展LCD显示器

1 引言

I2C总线是Philips公司推出的芯片间串行传输总线。它仅用串行数据线(SDA)和串行时钟线(SCL)两根连线便实现了完善的全双工同步数据传送,并可很方便地构成多机系统和外围器件扩展系统。

本文介绍在P87LPC764单片机中利用I2C总线系统中典型的LCD驱动控制器件PCF8577C来扩展256段静态LCD的电路设计方法。

2 硬件电路设计

2.1 P87LPC764单片机的I2C总线接口

P87LPC764是Philips公司生产的一种小封装、低成本、高性能的单片机(具体内容见参考文献2)。它采用80C51加速处理器结构,片内带有支持I2C总线的硬件接口。当激活I2C总线时,P87LPC764端口1中的P1.2与P1.3可分别用作SCL和SDA总线功能。其I2C总线由3个特殊功能寄存器控制,即I2C控制寄存器I2CON、I2C配置寄存器I2CFG、I2C数据寄存器I2DAT。各寄存器格式及位含义如下。

a.I2CON寄存器

I2CON寄存器各位的含义在进行读写操作时完全不同。下面分别介绍其读、写操作格式。

![]()

各位功能如下:

RDAT:数据接收位。在SCL线的上升沿时由SDA线上获取。读RDAT位时不清除DRDY,也不释放SCL线。

ATN:当DRDY、ARL、STR或STP中任意一个为1时,ATN置1。通过测试ATN位可判断总线上是否发生某类事件。

DRDY:数据准备好标志位。在SCL上升沿时置位,读写I2DAT寄存器或向CDR写入1时清0。 ARL:总线仲裁失败标志位。

STR:启动标志位。当检测到启动条件时置1。

STP:停止标志位。当检测到停止条件时置1。 MASTER:当本器件成为I2C总线主控器时置1。

![]()

其中:

CXA:写入1,清除数据发送状态。

IDLE:写入1,则被控制要检测到下一位启动位时才接收总线信息。

CDR:写入1,清除DRDY。

CARL:写入1,清除ARL。

CSTR:写入1,清除STR。

CSTP:写入1,清除STP。

XSTR:当装置为主控制器时,向XSTR和CDR写入1,使I2C总线发送重复启动位。

XSTP:当装置为主控制器时,向XSTP和CDR写入1,使I2C总线发送停止位。

![]()

b.I2CFG寄存器

SLA:写入1,本装置成为I2C总线被控器。

MASTRQ:写入1,本装置成为I2C总线主控器。

CTI:写入1,清除定时器1溢出标志。

TIRUN:写入1,定时器1开始运行;写入0,停止定时器1运行并将定时器清0。

CT1和CT0用来决定SCL线上高低电平的最小时间。

c.I2DAT寄存器

I2DAT寄存器的读、写格式是不同的。

其中RDAT为数据接收位。在SCL线的上升沿时从SDA中获取。在从I2DAT的RDAT中读数据的同时,可清除DRDY和设置发送激活状态。

其中XDAT为数据发送位。下一个要发送的数据写入此位。写XDAT时,应清除DRDY和设置发送激活状态。

2.2 I2C总线显示器件PCF8577C

a.引脚功能

PCF8577C是I2C总线系统中典型的LCD驱动控制器件,在静态方式时可驱动32段LCD;在双级方式时可驱动64段LCD。若采用多片级联,则最大可构成256段LCD显示系统。另外,PCF8577C还具有显示数据自动增量写入功能,而且编程十分简单。PCF8577的引脚排列如图1所示。各引脚功能如下:

S32~S1:段输出端口。

BP1:背极输出。级联时可作为同步输入端,接第一级的BP1信号作为同步信号。

A2/BP2:在静态驱动方式下,该端作为硬件地址线A2,用于设定8577C的硬件子地址。在双级驱动方式下,该脚用作第二背极输出BP2。级联时则作为同步输入端,接第一级的BP2信号作为同步信号。在双极方式下,其硬件子地址仅由A1和A0来决定。

A1:硬件地址线。片内无下拉电路,不可悬空。

A0/OSC:该脚需外接电阻电容来构成振荡器,此时A0被规定为逻辑0,用作硬件地址线。级联时,除第一级之外,其它各级均不外接电阻电容构成的振荡器,而应接VDD或VSS来设置器件子地址。

VDD和VSS:分别为电源正、负极。

SCL和SDA:分别为I2C总线的时钟和数据线。

b.数据操作格式

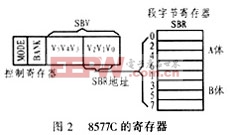

8577C有九个寄存器,其操作格式如图2所示。下面就控制寄存器和段字节寄存器加以说明。

●控制寄存器

控制寄存器用于在微处理机对8577C的一次数据传送过程中装入第二字节(控制字节)。控制字各位含义如下:

MODE:驱动方式选择位,“0”为选择静态驱动方式;“1”为选择双极驱动方式。

BANK:数据选择位,“0”为选择显示A体数据,“1”为选择显示B体数据。

V5V4V3:这三位与硬件子地址相对应。若器件的从地址与I2C总线上的从地址相符,且V5V4V3=A2A1A0,则该器件被选中,此时即可接收总线上送来的数据,并将其装入段字节寄存器,否则不予理睬。在双极驱动方式下,由于A2作BP2,故V5无效。

V2V1V0:段字节寄存器SBR的地址位,用来决定将段数据写入哪一个SBR。

用V5~V0可组成段字节向量SBV,它具有自动增量功能。若需一次传送多个段字节数据,可在每装入一个段字节数据后便SBV自动加2(静态方式)或加1(双级方式),以便装入下一个数据;级联时,当一片8577C装满后,SBV自动增量,并指向硬件子地址与之相邻的下一个8577C的SBR。SBV的值可以在111111~000000之间循环滚动。

●段字节寄存器SBR

八个SBR可分成两组,地址为偶数的一组称为A体,奇数组称为B体。在静态方式下,要么显示A体数据,要么显示B体数据。可以通过改变BANK位的值来切换显示内容。在双极方式下,八个SBR将同时使用,这时BANK为不关心码,A体对应于BP1,B体对应于BP2。

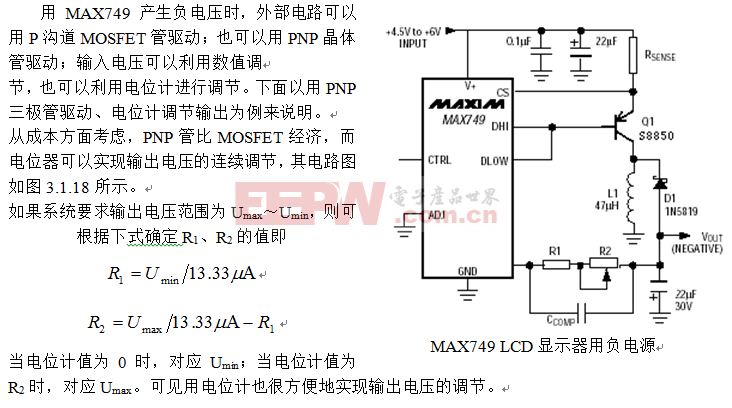

c.总线操作

PCF8577C的总线操作包括从地址和硬件子地址,其中从地址固定为0111010,共七位,是I2C总线委员会分配的。此外,还有三位硬件子地址(A2A1A0)待设定。若应用系统中有多片8577C,则需分别设定不同的硬件子地址来加以区别。选中8577C指的是它的从地址和硬件子地址都被选中。

![]()

其中:起始信号S之后的第一个字节中的最低位是方向位,因8577C只能接收数据,所以该位必须为0;其余七位是从地址。若系统含多片8577C,则每片都会对第一和第二字节作出应答;而段数据字节后的应答信号仅由被选中的芯片产生。数据字节可连续多个。如果仅改变BANK值,而不改变SBR中的内容,则应在控制字节的应答位之后发送停止信号P,这时被选中的芯片将更新BANK。

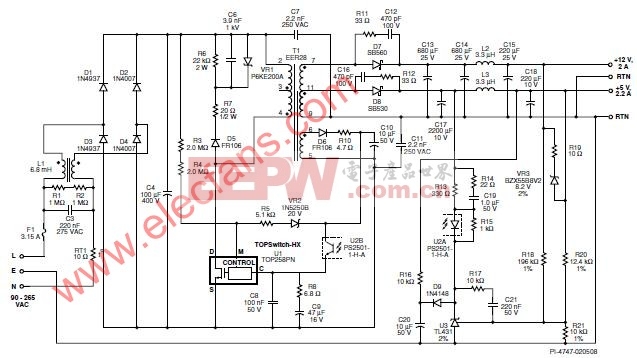

2.3 显示电路设计

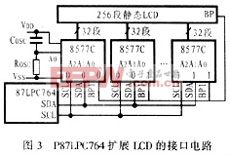

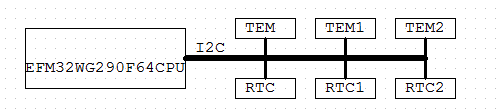

利用P87LPC764扩展LCD的接口电路如图3所示。该电路采用静态驱动方式,由P87LPC764单片机访问8片8577C以组成最大级联系统。每片8577C可驱动32段LCD,因此,共可扩展256段LCD。而在级联应用时,只由第一级构成振荡器,以输出背极信号,并对后级进行同步。

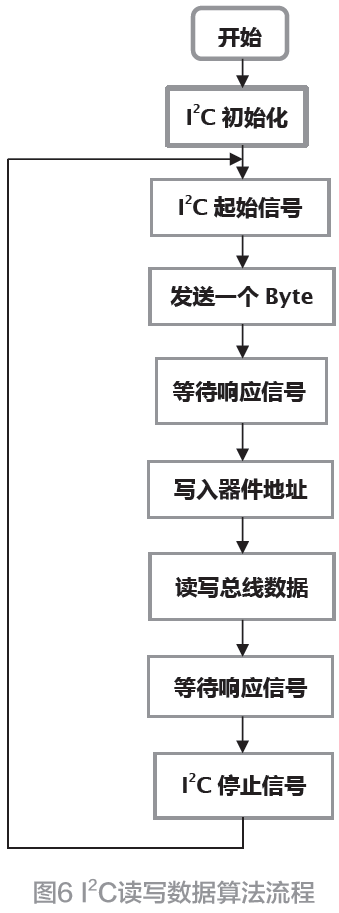

3 软件设计

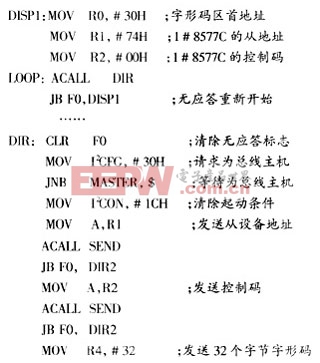

该应用电路是一个单主I2C总线系统,数据传送操作只有主发送方式,因而在编程过程中没有检测总线错误。数据发送时,每发送1个字节,都应检测应答信号,如无应答信号,建立标志位F0以重发数据。该电路采用静态方式,显示为A体数据。

如果程序中的显示缓冲区30H到7FH单元用来存放字形码,则该I2C总线显示电路的程序清单如下:

4 结束语

本文介绍了I2C总线系统中利用典型的LCD驱动控制器件PCF8577C扩展LCD显示器的电路及程序设计。参考本文思路,也可实现动态LCD显示器的扩展。该方法在I2C总线系统中进行人机接口电路设计时具有较好的参考价值。

评论