51单片机与串行AD转换器TLC0834的接口设计

单片机控制系统通常要用到A/D转换。根据输出的信号格式,比较常用的A/D转换方式可分为并行A/D和串行A/D。并行方式一般在转换后可直接接收,但芯片的引脚比较多;串行方式所用芯片引脚少,封装小,在PCB板上占用的空间也小,但需要软件处理才能得到所需要的数据。

1 TLC0834简介

1.1 TLC0834的主要特点

TLC0834是TI公司生产的8位逐次逼近模数转换器?具有输入可配置的多通道多路器和串形输入输出方式。其多路器可由软件配置为单端或差分输入,也可以配置为伪差分输入。另外,其输入基准电压大小可以调整。在全8位分辨率下,它允许任意小的模拟电压编码间隔。由于TLC0834采用的是串行输入结构,因此封装体积小,可节省51系列单片机I/O资源,价格也较适中。其主要特点如下:

● 8位分辨率;

● 易于和微处理器接口或独立使用;

● 可满量程工作;

● 可用地址逻辑多路器选通4输入通道;

● 单5V供电,输入范围为0~5V;

● 输入和输出与TTL、CMOS电平兼容;

● 时钟频率为250kHz时,其转换时间为32μs;

● 可以和美国国家半导体公司的ADC0834和ADC0838进行替换,但它内部不带齐纳稳压器网络;

● 总调整误差为±1LSB。

1.2 工作特点

TLC0834可通过和控制处理器相连的串行数据链路来传送控制命令,因而?可用软件对通道进行选择和输入端进行配置,其控制逻辑表如表1所列。

表1 TLC0834多路器的控制逻辑表

| 多路器地址 | 通 道 号 | ||

| SGL/DIF | ODD/EVEN | SELECT BIT1 | CH0 CH1 CH2 CH3 |

| L L H H | L H L H | L H L H | + - + - + - - + |

| H H H H | L L H H | L H L H | + + + + |

输入配置可在多路器寻址时序中进行。多路器地址可通过DI端移入转换器。多路器地址选择模拟输入通道可决定输入是单端输入还是差分输入。当输入是差分时,应分配输入通道的极性,并应将差分输入分配到相邻的输入通道对中。例如通道0和通道1可被选为一对差分输入。另外,在选择差分输入方式时,极性也可以选择。一对输入通道的两个输入端的任何一个都可以作为正极或负极。

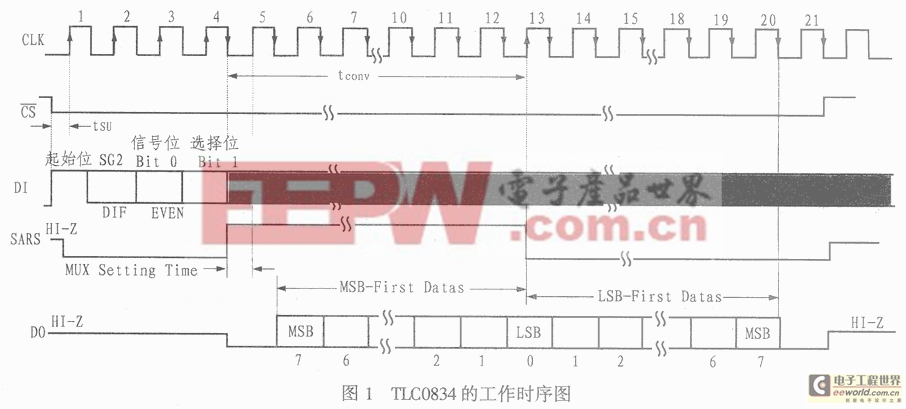

通常TLC0834在输出以最高位(MSB)开头的数据流后,会以最低位(LSB)开头重输出一遍(前面的数据流)。其工作时序如图1所示。

1.3 引脚功能

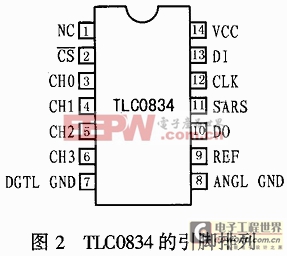

TLC0834的引脚排列如图2所示,其中CH0~CH3为模拟输入端; CS 为片选端;DI为串行数据输入,该端仅在多路器寻址时(MUX Settling Time)才被检测;DO为A/D转换结果的三态串行输出端;CLK为时钟;SARS为转换状态输出端,该端为高电平时,表示转换正在进行,为低电平则表示转换完成;REF为参考电压输入端;VCC为电源;DGTL GND为数字地,ANGL GND为模拟地。

2 与单片机的接口电路设计

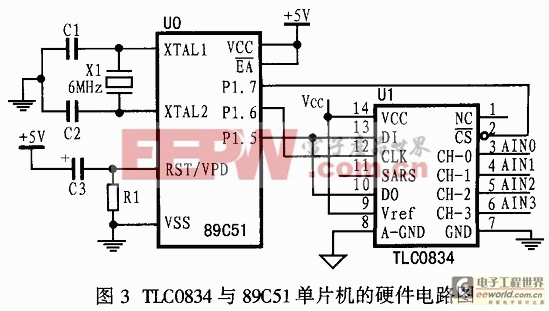

TLC0834与89C51单片机的硬件接口电路的电路原理如图3所示。图中,单片机的P1.7接TLC0834的片选信号, P1.6用于产生A/D转换的时钟, P1.5为一个双向I/O口位,可用于对模拟输入进行配置及输出转换所得的数据。在这里,模拟信号以单端方式输入,参考电压为5V,即A/D模拟量的输入范围为0~5V。

3 单片机的软件设计

该系统在工作时,单片机将通过编程产生串行时钟,并按时序发送与接收数据位,以完成通道方式/通道数据的写入和转换结果的读出。篇幅有限,现以通道0单端输入模拟信号为例,给出A/D转换的程序:

CLR P1.6 ;清时钟

CLR P1.5

SETB P1.7 ;置片选为高

CLR P1.7 ;置片选为低

SETB P1.5 ?1 Start Bit

SETB P1.6

CLR P1.6

SETB P1.5 ?1

SETB P1.6

CLR P1.6

CLR P1.5 ?0

SETB P1.6

CLR P1.6

CLR P1.5 ?0 CH0

SETB P1.6

CLR P1.6 ?通道0,单端输入

SETB P1.6

CLR P1.6

SETB P1.5 ?P1.5由输出状态改

为输入状态

LCALL ADCONV

···

···

···

ADCONV: MOV R0?#08H

ADLOP0: MOV C?P1.5 ;读转换结果

RLC A ;累加器A左移,将结果

逐位移入A中

STEB P1.6

CLR P1.6

DJNZ R0?ADLOP0

MOV R0?#07H

ADLOP1: SETB P1.6

CLR P1.6

DJNZ R0?ADLOP1

SETB P1.6

CLR P1.6

SETB P1.6

CLR P1.6

SETB P1.7 ;置片选信号为高,

结束一次转换

RET

转换结果经换算后可转换为十进制数显示出来。如在精度要求较高的场合,可以选用位数更多的串行A/D并取高位数据。限于篇幅,该部分程序本文不作介绍。

4 结论

本文给出的硬件和软件均经实践检验,并已在某公司的产品上应用,其性价比较高,可大大降低生产成本。

51单片机相关文章:51单片机教程

模数转换器相关文章:模数转换器工作原理

评论