S3C44B0X与C54X DSP的接口设计

1:S3C4510B简介

S3C4510B(以下简称4510)是韩国三星公司开发的一款基于ARM7TDMI架构的16/32位高性能微处理器。具用丰富的外围接口,如以太网,HDLC等,可灵活配置,适用于多种应用。4510具有以下性能特点:

◆ 8K字节的内部CACHE,也可用作内部SRAM

◆ 两线IIC接口,作为IIC主器件使用

◆ 以太网控制器

◆ 双通道HDLC控制器

◆ 双UART

◆ 双GDMA通道

◆ 两个32位定时器

◆ 18个可编程IO端口

◆ 中断控制功能

◆ 外部SDRAM/DRAM/FLASH/ROM控制

本文主要介绍4510中HDLC通道的使用和编程方法。

2:S3C4510B的HDLC通道简介

HDLC协议帧结构和特性请参阅相关书籍和4510数据手册,这里不详细介绍。

4510的HDLC通道结构如附图1所示。具有以下特点:

1. FIFO:发送和接收模块都有32字节(8字)FIFO,提供CPU内部总线到HDLC串行接口之间的数据缓存功能。

2. DMA:HDLC通道的发送和接收支持DMA方式。

3. 波特率产生:4510的HDLC通道包含一个可编程的波特率产生计数器,能够产生各种波特率的传输速率。

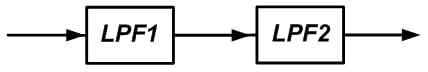

4. DPLL:4510的HDLC通道包含一个数字锁相环(DPLL),提供了时钟恢复功能,可从编码后的数据流中迅速提取出时钟信息。

5. 编码方式:4510的HDLC通道支持五种编码方式,分别为NRZ,NRZI,FM0,FM1和差分曼彻斯特编码,编码波形请参看附图2。

详细的内容请参阅4510数据手册。

3:S3C4510B的HDLC通道工作过程介绍

4510的HDLC通道收发可工作在CPU模式和DMA模式下,在我们的应用和编程中使用了DMA方式,因此这里主要介绍DMA方式下的工作过程。4510的HDLC通道工作过程大致可以分为通道初始化,数据发送,数据接收三个部分。

3.1: HDLC通道初始化过程

HDLC通道初始化过程可分为七个步骤;一:通道复位,恢复其默认配置;二:通过设置工作模式寄存器(HMODE)来配置HDLC工作模式;三:通过设置控制寄存器(HCON)来控制HDLC通道的工作;四:通过设置中断控制寄存器(HINT)来控制HDLC通道的中断产生;五:设置站址寄存器(HSAR0-HSAR3)和站址屏蔽寄存器(HMASK),以完成接收操作的地址比较功能;六:建立DMA方式的发送和接收BUFFER描述符链表结构,并初始化DMA发送BUFFER描述符指针寄存器(HDMATxPTR)和DMA接收BUFFER描述符指针寄存器(HDMARxPTR);七:使能HDLC通道的收发功能。

3.1.1:HDLC通道复位

HDLC通道复位可通过设置控制寄存器(HCON)前4比特来完成,请参阅4510数据手册。

3.1.2:HDLC通道工作模式配置

工作模式寄存器(HMODE)中的不同位定义了不同的工作模式,这里介绍较常用的几种模式设置,详细内容和配置方法请参阅4510数据手册。

1. 数据编码方式选择:从所支持的五种编码方式中选择。

2. 波特率时钟源选择:如果使用4510的内部波特率产生器,则需要为其选择时钟源,同时根据不同的时钟源配置波特率产生计数器(HBRGTC)产生需要的时钟信号。

3. DPLL时钟源选择:如果使用DPLL,则需要为其选择要跟踪的时钟源。

4. 发送时钟选择:4510的HDLC通道支持多种发送时钟源,可通过设置HDLC通道的模式寄存器中的相应位来选择。

5. 接收时钟选择:4510的HDLC通道支持多种接收时钟源,可通过设置HDLC通道的模式寄存器中的相应位来选择。

评论