片上系统芯片设计与静态时序分析

在集成电路设计技术已进入第四代的今天,一个电子系统或分系统可以完全集成在一个芯片之上,即系统芯片(SOC)集成。随着设计规模增大、电路性能的提高和设计的复杂度大大增加,相应地,对设计方法学提出了更高的要求。

传统的芯片设计中,只考虑了门本身的延迟,互连引起的延迟忽略不计,也正因如此,传统的设计流程可分为逻辑设计与物理实现两个相互独立阶段,芯片的设计考虑较简单。随着晶体管尺寸的降低,门的速度越来越快,限制电路性能提高的主要因素不再是开关速度,而是互连延迟。时钟频率越高,互连线作为扇出负载引起的延迟在整个时序预算中所占的比例越大。深亚微米设计范围中互连延迟占总延迟的60%~70%,因此精确地计算这部分延迟在芯片设计中是十分重要的。同时高性能电路使得所有时序的容差都非常小,也对精确定位电路各部分的延迟模型提出了更高的要求。另一方面,由于EDA(电子设计自动化)工具实现过程中互连延迟信息只有在物理实现后才能得到,而在深亚微米芯片设计中,只有用实际的布图拓扑信息约束逻辑设计,才能得到准确的时序。因此,为了提高芯片的设计效率,缩短设计周期,片上系统芯片设计(往往采用深亚微米工艺)必须克服传统设计方法中前端设计和后端设计相互分离的弊病。

另外,由于以往流行的动态时序验证是在验证功能的同时验证时序,需要输入向量作为激励。随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50%,且这种方法难以保证足够的覆盖率,因而对片上系统芯片设计已成为设计流程的瓶颈,所以必须有更有效的时序验证技术取代之。

2 片上系统芯片的设计流程

片上系统集成中越来越多地采用DSP或CPU核的设计方法,得到了世界各国EDA专家、学者的高度重视。SOC的设计涉及到算法、软件和硬件三方面问题。软硬件协同设计技术允许在设计早期进行软件和硬件的测试,及早地发现设计问题,因而成为当前的研究热点。但在系统层次上的软硬件协同设计方法仍有待于进一步深入研究。因为按现有的一般软硬件协同设计方法,在确定系统结构并完成软硬件的划分之后,用行为模型、RTL级硬件语言描述和数据通道合成的方法来完成硬件设计,用手工汇编和编译器来实现软件,系统重要参数则通过对该软硬件划分的协同模拟获得。因此系统结构的确定十分关键,但由于系统模型的多样性,人们不可能穷尽所有可能情况,也无法在系统级建立一个良好的模型设计策略。这样,较低层次的软硬件优化结果就难以保证完全符合整个系统优化的目标。对于高层次的自动化综合,一般自动化工具所采用的方法是首先根据系统的功能说明建立一个控制数据流图,然后通过调度和定位得到一条合适的数据路径。对于操作数量较低,芯片上功能单元较少的系统来说,该方法比较有效。但是对于诸如MPEG编码器的系统芯片,由于其操作量十分巨大,片上功能单元可能有数十个,在如此之多的操作和单元之间进行硬件的调度与映射,根本不可能利用完全自动化的方法实现,此外,在自动化验证流程中,软件的仿真时间也很长。因此,对复杂度较高的片上系统设计必须在更高抽象层次上开发软硬件协同设计策略。

片上系统在EDA工具上的实现流程也相应地变得更复杂了。随着特征尺寸的缩小,器件本身延迟不断减少(0.1um CMOS电路,典型门延迟为11.8ps)。同时,由于每单位长度的互连线电阻随着特征尺寸的缩小而不断变大,因此由互连线电阻和线电容引起的线延迟不断变大,在0.35um以下时,互连延迟甚至可达信号延迟的90%。因此,对于片上系统芯片在EDA工具上实现时,进行前端设计的同时必须考虑布图后互连的影响。

3 静态时序分析

仿真技术是ASIC设计过程中应用最多的验证手段,然而,现在的单片集成系统设计正在将仿真时间推向无法容忍的极限。在最后的门级仿真阶段,针对的是几十乃至几百万门的电路,对仿真器第一位的要求是速度和容量,因此,性能(仿真速度)和容量(能够仿真的设计规模)是验证中的关键因素,而此时仿真器还必须支持SDF返标和时序检查以确保验证的精度。

传统上采用逻辑仿真器验证功能时序,即在验证功能的同时验证时序,它以逻辑模拟方式运行,需要输入向量作为激励。随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50%,而最大的问题是难以保证足够的覆盖率。鉴于此,这种方法已经越来越少地用于时序验证,取而代之的是静态时序分析技术。

静态时序分析技术是一种穷尽分析方法,用以衡量电路性能。它提取整个电路的所有时序路径,通过计算信号沿在路径上的延迟传播找出违背时序约束的错误,主要是检查建立时间和保持时间是否满足要求,而它们又分别通过对最大路径延迟和最小路径延迟的分析得到。静态时序分析的方法不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少。它完全克服了动态时序验证的缺陷,适合进行超大规模的片上系统电路的验证,可以节省多达20%的设计时间。因此,静态时序分析器在功能和性能上满足了全片分析的目的。支持片上系统设计,即它为很快满足设计时序要求取得了突破,能提供百万门级设计所要求的性能,并在一个合理的时间内分析设计,而且它带有先进的时序分析技术和可视化的特性,用于全芯片验证。

4 设计实例与实验结果

我们以复杂度较高的电子系统——MPEG编码芯片系统为对象进行研究。图2是它的结构,其内部包含两个不同性质的可编程ASIP:高层为一个可编程性RISC核(结构见图3),除了协调各部分的操作之外,该核主要完成变长编码的算法任务;低层为一个高吞吐量的可编程数字信号处理器DSP核,该核主要用于运动估计、离散余弦变换和量化等细粒度的算法任务。此外,编码器内部还有专门的DMA(Direct Memory Access)控制器,用于管理片上存储器和片外存储器单元的数据交换。在此,着重研究该系统芯片上嵌入式RISC核的结构设计及EDA工具上的实现和静态时序分析。

研究表明,该RISC核在50MHz时钟频率下,就可以完成MPEG-2的变长编码任务。

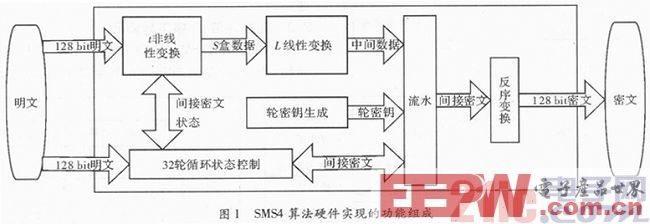

我们采用EUROPRACTICE的0.35μm CMOS低功耗库MTC45000系列,在Ultra SUN工作站上,引入Cadence的Floorplanning工具对版图进行整体规划,Synopsys Synthesis工具进行逻辑综合。按照图1的设计流程进行设计,其中运用Synopsys的PrimeTime对全芯片的门级静态时序进行了分析,完成了SOC设计的静态时序校验。

综合优化结果表明,该RISC核的电路规模为5500门左右(16个通用寄存器),动态功耗为20mW,时钟频率为73MHz,该RISC核完全达到了预期设计目标。表1给出了运用Synopsys的PrimeTime工具对关键路径的静态时序分析形成的报告(建立时间的验证)。结果表明该路径满足要求。需要指出的是,静态时序分析技术是一种穷尽分析方法,它提取整个电路的所有时序路径,限于篇幅,本文不再一一说明和罗列。

5 结束语

本文强调了片上系统芯片设计过程中必须在前端设计的同时考虑后端布图对时序的影响,并运用一个新的、全芯片的、门级静态时序分析工具支持片上系统设计,避免了由于芯片设计没有完全地被验证而导致了硅芯片失效的现象。实例设计表明,该设计方法能提高片上系统芯片设计中时序设计的准确性,提高验证效率,从而大大加快设计的收敛性。

评论