EmbeddedICE目标系统中的调试功能扩展部件

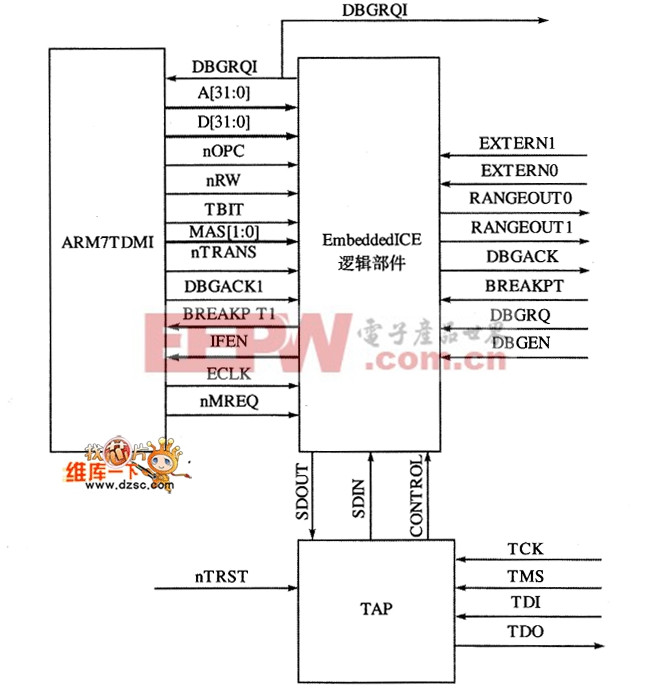

图 处理器内核、EmbeddedICE逻辑部件及TAP控制器之间的关系

EmbeddedICE逻辑部件包括:

·两个数据断点(watchpoint)寄存器。

·两个独立的寄存器,即调试寄存器和调试状态寄存器。

·调试通信通道(DCC)。

两个数据断点寄存器可以被用来设置断点或程序断点。当设置程序断点,地址与数据断点寄存器的值相等时,EmbeddedICE逻辑部件停止程序的执行;当前指定的当设置数据断点,当前数据总线上的数据与数据断点寄存器的值相等时,EmbeddedICE逻辑部件停止程序的执行。

与基于Angel的调试系统不同,这时程序断点可以设置在ROM中,这是因为EmbeddedICE逻辑部件提供了所需要的硬件支持。

在数据断点寄存器中的数据位可以被屏蔽,使其在进行比较时不起作用,从而使得断点的设置更为灵活。

调试通信通道(DCC)用来在主机上的调试器与目标处理器之间建立通信通道。在ARMTTDMI中,它是作为一个协处理器实现的。它包括:

·一个32位的通信数据读取寄存器。

·一个32位的通信数据写入寄存器。

·一个6位的通信控制寄存器。

通过这些接口,DOC可以在主机上的调试器和目标处理器之间建立通信信道。

在所有调试信号中,下面3个是最主要的。

●BREAKPT:终止处理器进入调试状态。

●DBGRQ:请求处理器进入调试状态。

●DBGACK:表明处理器己经进入调试状态。

评论