非易失闪存技术NAND Flash内存设备的读写控制设计

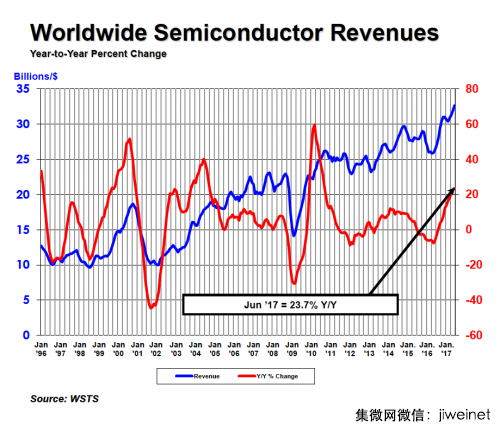

NOR Flash和NAND Flash是现在市场上两种主要的非易失闪存技术。Flash因为具有非易失性及可擦除性,在数码相机、手机、个人数字助理( PDA)、掌上电脑、MP3播放器等手持设备中得到广泛的应用。NAND Flash相对于NOR Flash具有更小的体积、更快的写入速度、更多次的可擦除次数以及更低廉的价格而得到了迅速发展。大容量的NAND Flash特别适合现在数码设备中大数据量的存储携带,可以降低成本,提高性能[1]。

1 系统设计1.1 NAND Flash和NOR Flash的区别

1.1.1 接口差别

NOR Flash带有SRAM接口,有足够的地址引脚来寻址,可以直接和CPU相连,CPU可以直接通过地址总线对NOR Flash进行访问,可以很容易地存取其内部的每一个字节。

NAND Flash器件使用复杂的I/O口来串行地存取数据,只能通过I/O接口发送命令和地址,对NAND Flash内部数据进行访问。各个产品或厂商的方法可能各不相同。8个引脚用来传送控制、地址和数据信息。NAND Flash读/写操作采用512或2 048字节的页。

NOR Flash是并行访问,NAND Flash是串行访问,所以相对来说,前者的速度更快些。

1.1.2 容量和成本

NOR Flash的成本相对高,容量相对小,常见的有128 KB、256 KB、1 MB、2 MB等;优点是读写数据时,不容易出错。所以在应用领域方面,NOR Flash比较适合应用于存储少量的代码。

NAND Flash的单元尺寸几乎是NOR Flash器件的一半,由于生产过程更为简单,也就相应地降低了价格。容量比较大,由于价格便宜,更适合存储大量的数据。

1.1.3 可靠性和耐用性

采用Flash介质时一个需要重点考虑的问题是可靠性。对于需要扩展MTBF的系统来说,Flash是非常合适的存储方案。可以从寿命(耐用性)、位交换和坏块处理三个方面来比较NOR Flash和NAND Flash的可靠性。寿命(耐用性)在NAND Flash闪存中每个块的最大擦写次数是一百万次,而NOR Flash的擦写次数是十万次。NAND Flash除了具有10∶1的块擦除周期优势,典型的NAND Flash块尺寸要比NOR器件小8倍,每个NAND Flash块在给定的时间内的删除次数要少一些。

1.1.4 位反转

NAND Flash和NOR Flash都可能发生比特位反转(但NAND Flash反转的几率远大于NOR Flash),因此这两者都必须进行ECC操作;NAND Flash可能会有坏块(出厂时厂家会对坏块做标记),在使用过程中也还有可能会出现新的坏块,因此NAND Flash驱动必须对坏块进行管理。

位反转对于用NAND Flash存储多媒体信息时倒不是致命的。当然,如果用本地存储设备来存储操作系统、配置文件或其他敏感信息时,必须使用EDC/ECC系统以确保可靠性。坏块处理NAND Flash器件中的坏块是随机分布的。NAND Flash器件需要对介质进行初始化扫描来发现坏块,并将坏块标记为不可用。

1.1.5 易于使用

NAND Flash不能在片内运行程序,而NOR Flash可以。但目前很多CPU都可以在上电时以硬件的方式先将NAND Flash的第一个BLOCk中的内容(一般是程序代码,也许不足一个Block,如2 KB大小)自动拷贝到RAM中,然后再运行。因此,只要CPU支持,NAND Flash也可以当成启动设备。由于需要I/O接口,NAND Flash要复杂得多。各种NAND Flash器件的存取方法因厂家而异。在使用NAND Flash器件时,必须先写入驱动程序,才能继续执行其他操作。

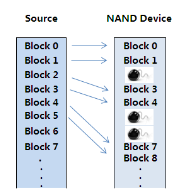

1.2 NAND Flash的存储结构

大多数的NAND Flash都大同小异,所不同的只是该NAND Flash芯片的容量大小和读写速度等基本特性。

块Block是NAND Flash的擦除操作的基本/最小单位。页是读写操作的基本单位。

每一个页,对应还有一块区域,叫做空闲区域/冗余区域,而在Linux系统中,一般叫做OOB(Out Of Band)[2]。这个区域最初基于NAND Flash的硬件特性,数据在读写时候相对容易出错,所以为了保证数据的正确性,必须要有对应的检测和纠错机制,此机制被叫做EDC(Error Detection Code)/ECC(Error Code Correction)。所以设计了多余的区域,用于放置数据的校验值。OOB的读写操作一般是随着页的操作一起完成的,即读写页的时候,对应地就读写了OOB。OOB的主要用途: 标记是否是坏块,存储ECC数据,存储一些和文件系统相关的数据。

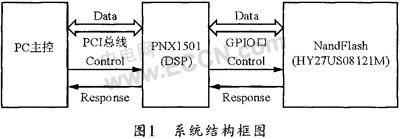

1.3 NAND Flash的接口控制设计

系统中选用的NAND Flash为海力士半导体公司(Hynix)的H27U1G8F2B[3],它是一个1 GB的内存,每页的大小为2 112字节(2048+64备用),每个块的大小为128K+4K备用字节。H27U1G8F2B的8个I/O引脚是地址复用的,这样可以减少引脚数,并方便系统升级,闪存的电源为33 V。NAND Flash H27U1G8F2B的接口控制电路如图1所示。

图1 NAND Flash控制电路

由于NAND Flash只有8个I/O引脚,而且是复用的,既可以传数据,也可以传地址、命令。设计命令锁存使能(Command Latch Enable, CLE) 和 地址锁存使能(Address Latch Enable,ALE),就是先要发一个CLE(或ALE)命令,告诉NAND Flash的控制器一声,下面要传的是命令(或地址)。这样,NAND Flash内部才能根据传入的内容,进行对应的动作。相对于并口的NOR Flash的48或52个引脚来说,大大减小了引脚数目,这样封装后的芯片体积小。同时,减少了芯片接口,使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

2 软件设计

2.1 NAND Flash的读写控制

Linux MTD[4]对NAND Flash芯片的读写主要分三部分:

① struct mtd_info中的读写函数,如read、write_oob等,这是MTD原始设备层与Flash硬件层之间的接口。

② struct nand_ecc_CTRl中的读写函数,如read_page_raw、write_page等,主要用来做一些与ECC有关的操作。

③ struct nand_Chip中的读写函数,如read_buf、cmdfunc等,与具体的NAND controller相关,就是这部分函数与硬件的交互。

这三部分读写函数是相互配合着完成对NAND Flash芯片的读写的。首先,MTD上层需要读写NAND Flash芯片时,会调用struct mtd_info中的读写函数;接着,struct mtd_info中的读写函数就会调用struct nand_chip或struct nand_ecc_ctrl中的读写函数;最后,若调用的是struct nand_ecc_ctrl中的读写函数,那么它又会接着调用struct nand_chip中的读写函数。读写相关函数如图2所示。

2.2 NAND Flash的读页流程

2.2.1 读页时序

读页流程如图3所示。可以看到如果要实现读一个页的数据,就要发送Read的命令,而且是分两个周期,即分两次发送对应的命令。第一次是00h,第二次是30h,而两次命令中间,需要发送对应的你所要读取的页的地址。 图4为读页时序。

评论