车载信息的硬件电路设计

主控模块的处理器采用三星公司的S3C2410,以其为核心扩展64MB的Nand-Flash和2MB的Nor-Flash用于存放启动代码、嵌入 式Linux操作系统等,64MB的SDRAM用做系统运行时的内存,LCD提供了更好的人机交互界面。

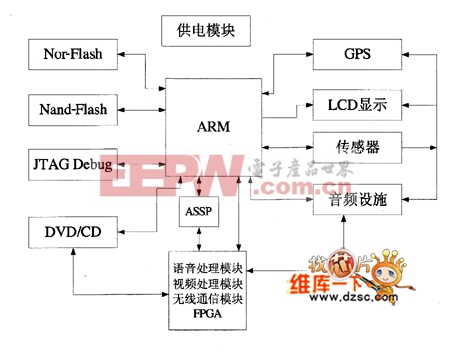

硬件结构图如图1所示。

图1 硬件结构图

ARM微控制器作为核心控制电路,作为硬件系统的中枢控制中心,主要用于协调和管理系统中的其他硬件。核心控制电路 具备丰富的接口电路,以满足不同子模块的不同接口要求。

FPGA协处理器,可以负责完成车载信息系统中各子模块中算法要求高编程处理性能。例如,对于各种音频/视频流媒体等 高速数字信号的处理,以及无线通信、语音识别等。

2 硬件模块说明

图1给出了硬件结构图,本节将会重点介绍几个硬件模块。

(1)GPS模块接口设计

GPS接收机采用GARMIN公司的GPS25-LVC接收机,其内置了GPS25OEM板。GPS25-LVC接收机采用+5V供电,内置保护电池, 具有两个RS-232兼容TTL串行口(串口1传输NMEA语句,串口2输出相位数据),可自动输出NMEA0 1 83语句,用户可选择波 特率1200/2400(只发)/4800/9600bps;同时支持RTCM差分输入。GPS25 OEM板接口信号表如表1所示。

表1 GPS25 OEM接口信号表

GPS25-LVC接收机从硬件上十分易于使用,由于本系统位置信息选用NMEA语句,通过串行口1的4脚输出数据,5脚是一个 输入引脚,用于对GPS25-LVC进行设置。设计中没有使用GPS25-LVC的标准时钟脉冲信号。

评论