51单片机复位电路的设计

单片机在可靠的复位之后,才会从0000H地址开始有序的执行应用程序。同时,复位电路也是容易受到外部噪 声干扰的敏感部分之一。因此,复位电路应该具有两个主要的功能:

1. 必须保证系统可靠的进行复位;

2. 必须具有一定的抗干扰的能力;

一、复位电路的RC选择

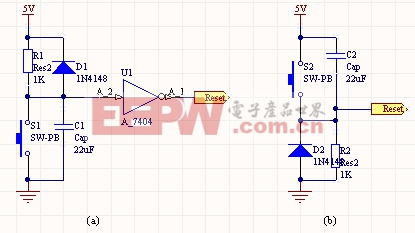

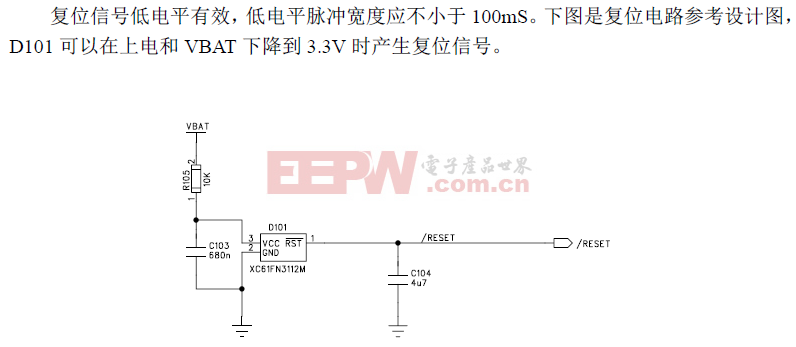

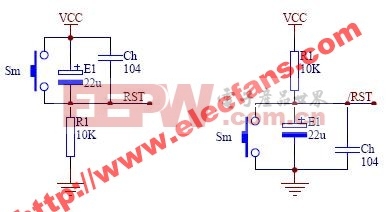

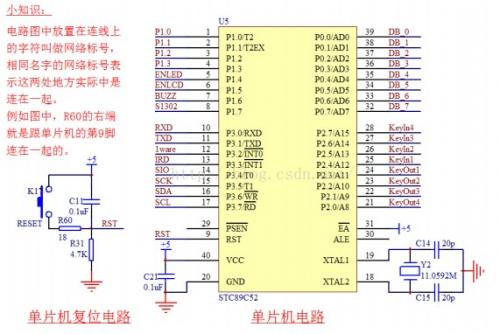

复位电路应该具有上电复位和手动复位的功能。以MCS-51单片机为例,复位脉冲的高电平宽度必须大于2个机器周期,若系统选用6MHz晶振,则一个机器周期为2us,那么复位脉冲宽度最小应为4us。在实际应用系统中,考虑到电源的稳定时间,参数漂移,晶振稳定时间以及复位的可靠性等因素,必须有足够的余量。图1是利用RC充电原理实现上电复位的电路设计。实践证明,上电瞬间RC电路充电,RESET引脚出现正脉冲。只要RESET端保持10ms以上的高电平,就能使单片机有效的复位。

图 1

对于图1-a中的电容C两端的电压(即复位信号)是一个时间的函数:

u(t)=VCC*[1-exp(-t/RC)]

对于图1-b中的电阻R两端的电压(即复位信号)也是一个时间的函数:

u(t)=VCC*exp(-t/RC)

其中的VCC为电源电压,RC为RC电路的时间常数=1K*22uF=22ms。有了这个公式,我们可以更方便的对以上电路进行透彻的分析。

图1-a中非门的最小输入高电平UIH=2.0v,当充电时间t=0.6RC时,则充电电压u(t)=0.45VCC=0.45*5V,约等于2V,其中t即为复位时间。图a中时间常数=22ms,则t=22ms*0.6=13ms。

二、复位电路的可靠性与抗干扰性分析

单片机复位电路端口的干扰主要来自电源和按钮传输线串入的噪声。这些噪声虽然不会完全导致系统复位,但有时会破坏CPU内的程序状态字的某些位的状态,对控制产生不良影响。

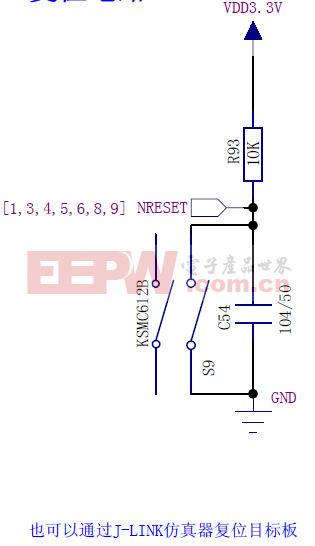

1.电路结构形式与抗干扰性能

以图1为例,电源噪声干扰过程示意图如图2种分别绘出了A点和B点的电压扰动波形。

有图2可以看出,图2(a)实质上是个低通滤波环节,对于脉冲宽度小于3RC的干扰有很好的抑制作用;图2(b)实质上是个高通滤波环节,对脉冲干扰没有抑制作用。由此可见,对于图1所示的两种复位电路,a的抗干扰电源噪声的能力要优于b。

2. 复位按钮传输线的影响

复位按钮一般都是安装在操作面板上,有较长的传输线,容易引起电磁感应干扰。按钮传输线应采用双绞线(具有抑制电磁感应干扰的性能),并远离交流用电设备。在印刷电路板上,单片机复位端口处并联0.01-0.1uF的高频电容,或配置使密特电路,将提高对串入噪声的抑制能力。

电路相关文章:电路分析基础

51单片机相关文章:51单片机教程

单片机相关文章:单片机教程

单片机相关文章:单片机视频教程

单片机相关文章:单片机工作原理

双绞线传输器相关文章:双绞线传输器原理

评论