浅谈AT91RM9200的嵌入式网络摄像机的设计与实现

随着通信技术和网络技术的迅猛发展,通过网络远程实时监控重要场所已倍受人们关注,网络摄像机在此背景下产生,并成为人们关注的焦点。网络摄像机是一种结合传统摄像机与网络技术所产生的新一代摄像机,它可以将影像通过网络传至地球另一端,且远端的浏览者不需用任何专业软件,只要标准的网络浏览器(如"Microsoft IE或Netscape)即可监视其影像。网络摄像机要将高清晰度的实时视频信息通过互联网传送到监控终端,因其信息量巨大,所以必须压缩。通常人们采用DSP与MPEG-4算法相结合的方案来实现,不仅编程工作量大,而且产品的成本高。本文所介绍的网络摄像机采用专用的MPEG-4压缩芯片、以嵌入式Linux作为操作系统,不仅开发便捷、成本低廉,而且实时性好,适用范围广。

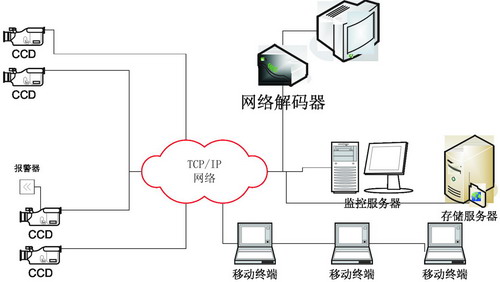

2. 系统总体设计

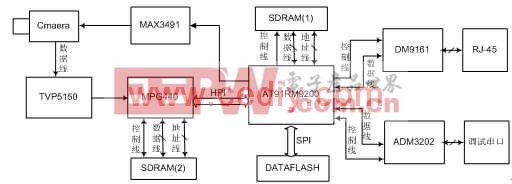

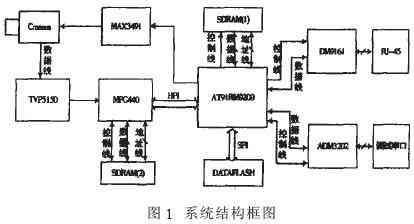

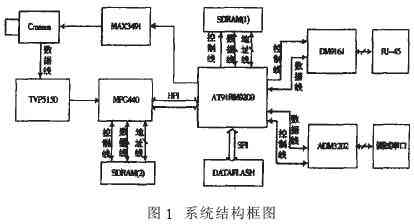

系统总体设计包括硬件设计和软件设计两部分。这两部分工作是互相联系的,需要交叉进行,系统设计是开发人员进行的工作,他们将系统设计阶段得到的目标系统的逻辑模型转换为目标系统的物理模型,该阶段得到工作成果――系统设计说明书是下一个阶段系统实施的工作依据。硬件设计模块主要包括微控制器模块、微控制器是将微型计算机的主要部分集成在一个芯片上的单芯片微型计算机。微控制器诞生于20世纪70年代中期,经过20多年的发展,其成本越来越低,而性能越来越强大,这使其应用已经无处不在,遍及各个领域。例如电机控制、条码阅读器/扫描器、消费类电子、游戏设备、电话、HVAC、楼宇安全与门禁控制、工业控制与自动化和白色家电(洗衣机、微波炉)等。压缩编码模块、网络接口模块和相机控制模块四部分。微控制器模块主要由主控芯片、DataFlash和SDRAM(1)组成。其中,主控芯片是整个控制系统的核心,它负责整个系统的调度工作。DataFlash里固化了嵌入式Linux内核、及其文件系统、应用软件和系统配置文件。压缩编码模块由视频数据采集芯片、MPEG-4压缩编码芯片、SDRAM(2)组成,负责将视频流转化为MPEG-4码流。网络接口模块主要是配合主控芯片传送MPEG-4码流。相机的控制模块主要由串口芯片组成,其完成转发控制相机命令的功能。当系统启动时,微控制器通SPI(Serial Peripheral Interface,串行外设接口)将Linux内核转入SDRAM(1)中,系统从SDRAM(1)中启动。系统启动后,微控制器通过HPI(Host Peripherial Interface, 主机接口)控制MPEG-4编码模块。统结构如图1所示。

图1 系统结构框图

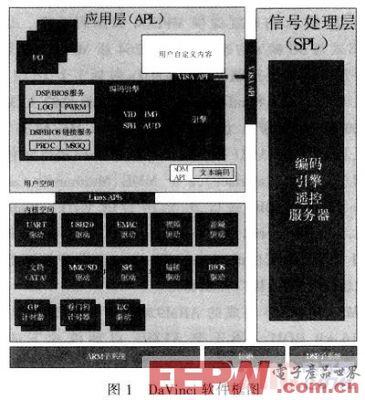

软件设计部分主要包括嵌入式Linux移植、MPEG-4压缩编码模块、CGI控制程序和MPEG-4解码程序四部分。嵌入式Linux系统存放到由AT91RM9200控制的DataFlash里,它负责整个系统软件的调度工作。MPEG-4压缩编码模块主要负责模拟视频流的采集,并将数字视频流压缩为MPEG-4数据流。CGI控制程序主要负责对摄像机的控制和对MPEG-4视频流的相关设置。简称CGI.在物理上是一段程序,运行在服务器上,提供同客户端 HTML页面的接口。这样说大概还不好理解。那么我们看一个实际例子: 现在的个人主页上大部分都有一个留言本。留言本的工作是这样的:先由用户在客户端输入一些信息,如名字之类的东西。接着用户按一下"留言"(到目前为止工作都在客户端),浏览器把这些信息传送到服务器的CGI目录下特定的cgi程序中,于是cgi程序在服务器上按照预定的方法进行处理。在本例中就是把用户提交的信息存入指定的文件中。然后cgi程序给客户端发送一个信息,表示请求的任务已经结束。此时用户在浏览器里将看到"留言结束"的字样。整个过程结束。MPEG-4解码程序主要负责对通过网络得到的MPEG-4数据流的解码工作。

3. 硬件设计

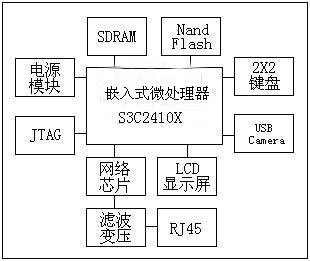

3.1微控制器模块

微控制器是本系统的核心部件,选用的是ATMEL公司的AT91RM9200.它是一款基于ARM920T核的32位微控制器。其主频为180MHz,处理速度快,功能强,性价比高,能很好满足嵌入式Linux系统的需求。它在系统中的主要作用是在系统上电时配置其他芯片的功能寄存器,在正常工作状态下调度控制整个系统工作,通过片内以太网控制器控制物理层芯片发送码流。

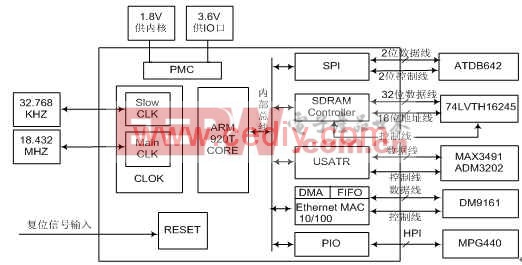

AT91RM9200通过片内的SPI总线和SDRAM控制器实现对外围DataFlash和SDRAM的控制,利用片内的USART实现对串口芯片的控制,通过片内的以太网控制器对片外网络芯片进行控制。其控制原理图如图2所示。

图2 控制原理图

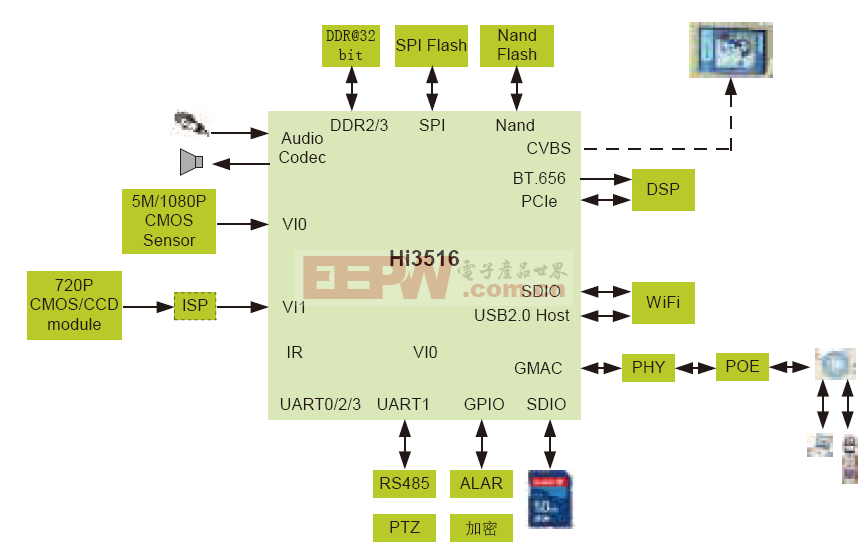

3.2压缩编码模块

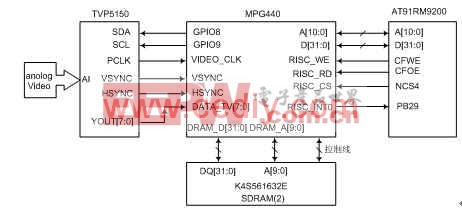

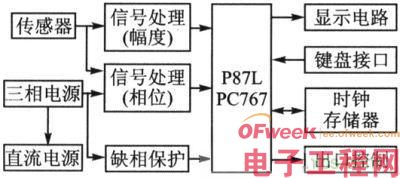

压缩编码模块包括模拟视频采集模块和MPEG-4压缩模块。视频采集芯片采用TI公司的TVP5150,数据压缩芯片采用映佳公司的MPG440.TVP5150输入端可是两种混合视频信号也可是S-Video端子的视频信号,支持NTSC、PAL、SECAM等3种制式,其输出的数据色彩格式可以为8bit 4:2:2数字信号或者8bit同步ITU-R BT.656数字信号。MPG440芯片具有符合工业标准的16b/32b的双向主机接口,分别用来与视频采集芯片和微控制器芯片通信。同时,具有移动侦测、防伪水印、动态调整IP画格比率、动态调整图像质量等特性,支持D1、VGA、CIF、QVGA、QCI等五种分辨率模式。微压缩编码模块的硬件设计原理如图3所示。

图3 压缩编码电路

TVP5150的AI模拟输入口与模拟摄像头输出端连接,向视频处理芯片传送模拟视频信号。模拟信号经过采样处理之后通过YOUT0~YOUT7引脚送到MPG440,采样数据在PCLK的上升沿有效,MPG440的VIDEO_CLK在收到PCLK的上升沿时获得YOUT的信号。TVP5150分场同步脉冲和行同步脉冲,分别对应其输出端VSYNC、HSYNC.MPG440正是根据与之相连的VSYNC和HSYNC信号线来实现图像的场同步和行同步操作。MPG440的视频输入数据线DATA_TV0~DATA_TV7与TVP5150的YOUT0~YOUT7相连。MPG440在接收数据的同时,将其得到的数据流传送给MPEG-4压缩编码单元,编码后的MPEG-4数据流暂存到SDRAM(2)中。MPG440片内PDMA控制器根据配置寄存器的设置准确发起对SDRAM(2)访问,同时将得到的数据流输送往HPI(主机总线接口,Host Peripherial Interface),以等待AT91RM9200通过DMA通道将数据发送到网络。

MPG440通过HPI与AT91RM9200通信,AT91RM9200将MPG440的寄存器、存储空间等资源作为其本身内存寻址访问。MPG440由AT91RM9200选通线NCS4来选通,其在AT91RM9200寻址空间中的地址段为0X50000000到0X5FFFFFFF.通过对MPG440一系列寄存器的设置,可以访问MPG440系统存储空间。MPG440中断信号RSC_INT0从通用I/O引脚的PB29输入,当缓冲器填满时,RSC_INT0引脚置低提示AT91RM9200通过DMA通道提取MPEG-4数据流。编码后视频数据读取过程和MPG440与主机通信过程由AT91RM9200读信号CFRD和写信号CFWE控制。

评论