基于ATMEGA128的自动准同期装置设计

自动准同期装置在电力系统并网中有着十分重要的作用。本文采用ATMEGA128单片机为处理器,开发一种主要用于机组同期操作的自动准同期装置,该装置能自动检测系统侧和对象侧的压差、频差和相差,进行同期操作。如果采用一个同期点配备一个装置的方式,则能大大提高整个系统的同期可靠性。

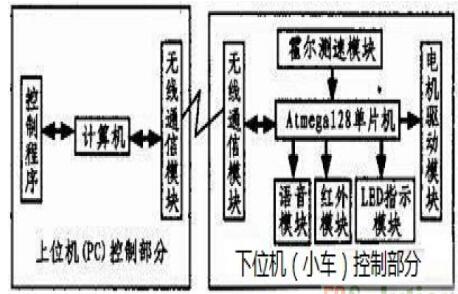

1 系统的总体设计和硬件框图

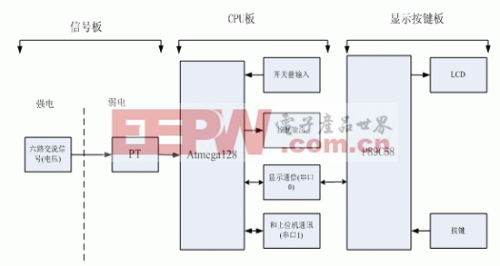

作为准同期装置,首先必须要准确地测量系统侧和待并侧的同期参数。也就是精确测量两侧的电压、频率,以及相位差。在这个基础上,装置要进行准确的同期动作以及和上位机的通信。因此,系统的硬件设计和软件流程围绕这三个方面展开。为了减少干扰和便于操作,硬件分为CPU板、信号板和显示按键板。下面的硬件框图清楚地表示了三者之间的连接关系和信号的流动情况。

图1 系统硬件框图

单片机89C58主要负责识别和保存按键值(中断方式),以及直接驱动LCD。

Atmega128单片机有两个串行口,通过串口0和89C58通讯,通过串口1和上位机进行数据交换。

2 频率、电压和相差的计算

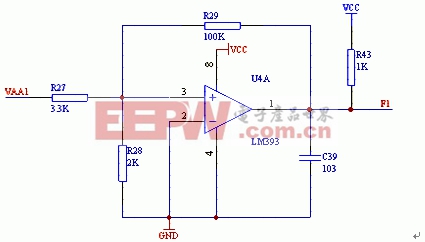

ATMEGA128单片机的定时器1和定时器3具有输入捕获的功能。因此频率(周期)的计算可以完全依赖硬件来实现。只需要设计一个转换电路将正弦波变换成为方波即可。方波两个上升沿(或下降沿)之间的时间间隔即是系统侧或对象侧的周期,这样就可以准确地测量出周期。注意,定时器1和定时器3中的计数值尽量不要采用软件清零。笔者刚开始的思路是每隔一次输入捕获中断将TCNT1或TCNT3的值清零,然后下一次的计数值乘以计数间隔时间就是系统侧或是对象侧周期长度。但是这样的办法很容易受到其他中断的影响。当外部事件发生的时候(上升沿或下降沿来到),硬件自动将计数值捕捉到相应的捕获寄存器,但如果此时有更高级中断同时到来的话,就必然会推迟一会才可以进入输入捕获中断程序,则软件必然会推迟清零,因此所测的周期会偏小、频率会偏大。特别是当更高优先级的中断程序执行时间较长时,所测周期根本无法使用。正确的做法是:在初始化时将定时器1和定时器3按照同样的分频系数同时开放,然后就不要对这两个定时器进行清零或其他操作。对于这两个16位定时器的溢出问题,可以通过在定时器1和定时器3的溢出中断程序中设置分别的溢出标志来解决。本装置所设计的波形转换电路如图2 所示。VAA1为对象侧或系统侧经过初步处理的交流信号。

图 2

电压的测量和计算涉及到交流采样技术。交流采样,就是直接对交流电气信号的瞬时值进行采样,再用一定的数值算法求得所关心的信号参数或信息。交流采样有异步采样和同步采样两种,其中后者应用较多。同步采样又可以分为硬件同步(PLL锁相环技术)和软件同步。软件同步就是利用处理器的中断性能跟踪周期的变化且均匀地采样。这就是所谓的频率跟踪。在数据处理方面,本文采用将正弦周期信号展开成为傅立叶级数的形式,然后再离散化,进而求出电压有效值。

评论