SoC验证走出实验室良机已到

SoC验证超越了常规逻辑仿真,但用于加速SoC验证的广泛应用的三种备选方法不但面临可靠性问题,而且难以进行权衡。而且,最重要的问题还在于硬件加速访问权限、时机及其稳定性。

本文引用地址:http://www.amcfsurvey.com/article/215718.htm当前,通常采用的三种硬件方法分别是FPGA原型验证、采用验证IP进行的加速仿真以及内电路仿真(ICE)。这些方法虽适用于某些情况,但对于那些面对不断更新的多处理器、多协议且偏重于软件的SoC验证团队来说,则存在明显不足。

FPGA原型验证适用于那些运行于不再进行更新的已有硬件上的软件,但却不适用于仍在进行大规模升级的硬件。其原因在于设计流程不同步:硬件完成后,软件团队方可使用FPGA开发板,而且一旦出现问题,重新编译耗时动辄数以天计,绝非几个小时便可完成。此外,试图将有数百万个门电路的SoC分解到几个FPGA上无异于自讨苦吃。因此,尽管FPGA原型验证看起来成本低廉,但对于仍在进行硬件调试的SoC来说,这一过程耗时漫长且充满风险。这也正是在仿真市场的年增长速度高达20%的同时,这一市场却波澜不兴的原因。

加速仿真 — 采用深测试序列、代码覆盖、基于断言的验证、错误处理、协议检查等方法 — 适用于需对新开发的无漏洞ASIC或基础IP进行验证的硬件开发人员。但是,在对由软件驱动且多个现有硬件模块须同时工作的SoC进行验证时,则需要一种整个软件团队均可使用的验证方法。嵌入式处理器经测试后方可加载软件。

直至2012年,内电路仿真(ICE)仍是进行软硬件协同验证的唯一方法,且在原型硬件可用前,需经常对硬件进行更改。ICE适用于规模相对较小的项目团队,团队成员集中于一处,对实验室享有个人完全控制权,设计所含硬件目标接口数量有限。但由于需对运行于与实验室内仿真器相连接的外部硬件上的目标外设或主机进行建模,因此在适应性、可靠性以及ROI等方面存在严重缺陷。

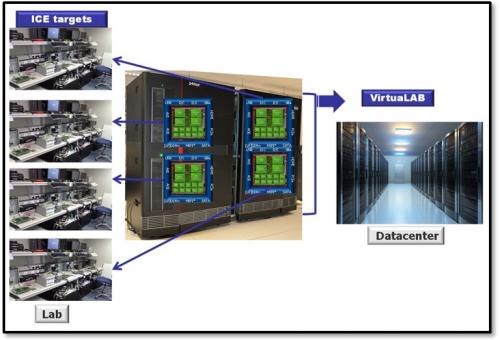

线缆以及外部硬件设备不但提高了复杂度,带来了可靠性隐患,而且限定了仿真方式,因此实验室的设置成为瓶颈环节。在进行内电路仿真时,属于不同项目组的多个远程软硬件工程师团队同时进行仿真的唯一方法是,在多个仿真器上运行同一项目设置。这样做不但成本高昂、能耗极大,而且不易于管理。

幸运的是,目前已有第四种方法可用,即利用“虚拟实验室”仿真环境。虚拟实验室更适用于成员领域各异、挑战错综复杂,且面临相同的SoC开发难题的大型团队。

由于虚拟仿真实验室具有可以向所有软件工程师提供灵活仿真器、免去了由于布置线缆而造成的杂乱无章、不会因如RAID般的多个内电路仿真装置同时运行而造成高能耗等优点,因此为满足SoC设计团队对虚拟仿真实验室的需求,这一新方法应运而生。很显然,该解决方案需进行多次软件验证过程。

将仿真从实验室转移至数据中心进行可提升产能,增强灵活性,提高可靠性。

在10余年协同模型研究的基础上,Mentor Graphics公司于2012年宣布,一种全新的仿真方法研发成功。该方法摆脱了对目标外设的外部硬件设备运行模型的依赖,取而代之的是,允许客户将仿真器置于通用数据中心,并且仅需将其视为另一种计算资源。

采用这一全新仿真方法,设计师可以将其目标协议与设计同时加载于仿真器,并通过个人电脑驱动测试流程的软件层,而真正的目标操作系统、驱动程序以及应用程序则在一台虚拟机上安全运行。

与其他方法相比,当软硬件处于开发早期阶段,且更改频繁时,更适宜采用该虚拟实验室解决方案进行SoC验证。对于所含门电路达数以百万计的嵌入式处理器,多种外设,以及复杂软件测试,虚拟实验室的灵活性和生产效率均得到大幅提高。

从功能上讲,虚拟实验室和内电路仿真器相同,但更多的测试流程在软件中进行。可通过个人电脑或工作站进行控制,且提供了与ICE解决方案中所用模型相同的硬件精确模型,并有适当的预验证IP可供工程师使用。协议RTL模型、软件栈以及应用程序可轻松地下载至仿真器,强化SoC验证流程。和ICE类似,软件工程师可通过虚拟实验室访问仍处于RTL阶段的硬件设计,但方式更灵活,即无需通过繁冗设置,且无需在仿真器停机时间进行。

对于硬件工程师来说,将仿真器从实验室移至数据中心,可避免因布线变动、引脚损坏、可用引脚缺乏以及远程实验室工作人员对外部目标硬件进行倒线时的彻夜等待而导致的停机。有了虚拟实验室仿真,工程师的测试工作可不再依靠定制目标板进行。

对于软件工程师来说,它则为在虚拟机上运行真正的目标操作系统提供了一个稳定性更好、灵活性更强的环境。比如,代码请求内存不可用时,不会再出现硬件崩溃现象;电脑仍可正常工作,仅需虚拟机重新启动。

ROI亦随着对仿真器的访问而得到提高。在虚拟实验室环境下,仿真器被视作一台服务器,可供多个团队、多个项目组,甚至处于不同地理位置的人员使用。它不再是一台只可供少数特殊人群使用的昂贵设备。其目标是,同时为同一企业的各个项目组的所有软硬件及集成工程师提供一个永远在线的高度灵活的仿真环境。

通过同步工程实现ROI、质量以及生产效率的提升已走过了漫长历程。通过将SoC验证移出实验室,虚拟实验室仿真创造的验证环境最终使得上述目标成为现实。

Richard Pugh拥有25年以上的电子设计自动化经验,曾在ViewLogic、Synopsys和Mentor Graphics公司的应用工程、产品营销以及业务拓展岗位上从事IP、ASIC以及SoC验证工作。目前,他担任Mentor公司仿真部产品营销经理。Richard持有伦敦大学学院计算机科学与电子学硕士学位,以及悉尼麦考瑞大学管理学院工商管理硕士学位。

评论