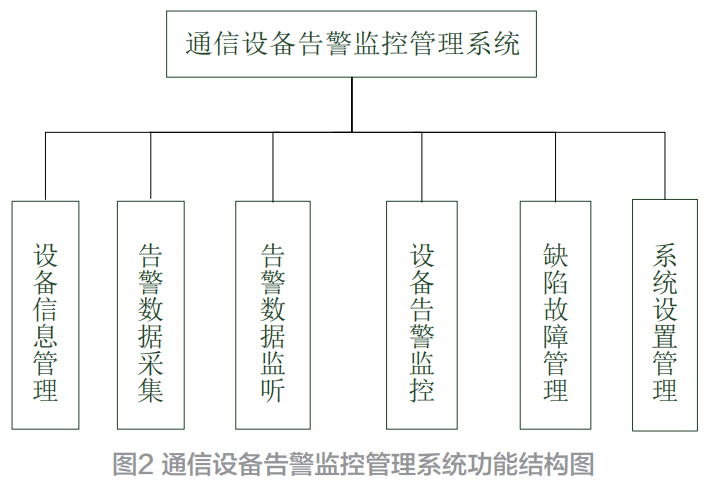

基于USB接口的高增益数据采集系统的设计

0 引言

在现代工业生产和科学技术研究等各行业中,通常需要对各种数据进行采集。目前常用的通过数据采集板卡采集的方法存在着以下缺点:安装麻烦,易受机箱内环境的干扰而导致采集数据的失真,容易受计算机插槽数量和地址、中断资源的限制,可扩展性差。而带RS-232串口的数据采集器,在需要大批量、高速传输的场合下,其应用也受到限制。通用串行总线USB(Universal Serial Bus)的出现,很好地解决了上述问题,很容易实现便捷、高速、低成本、易扩展、高可靠性的数据采集,代表了现代数据采集系统的发展趋势。

1 硬件设计与实现

USB总线传输速度快,为了充分发挥USB总线这一优势,易选用速度较快的微处理器。另外,USB接口设备是采用总线供电的,考虑到总线输出功率有限,尽量采用集成度高的器件有利于降低USB总线的负荷。

USB接口模块的选择有两种方案:一种是采用带有USB接口的单片机;另一种是采用普通单片机和USB控制芯片。对于第一种方案,不需要设计单片机和USB控制芯片之间的接口电路,简化了电路设计,但是带有USB接口的单片机种类有限,从而限制了单片机的选择。对于后一种方案,可以选择所熟悉的单片机,以减小开发难度,并缩短开发周期。系统采用的是SOC单片机C8051F000,USB控制芯片采用PDIUSBD12。

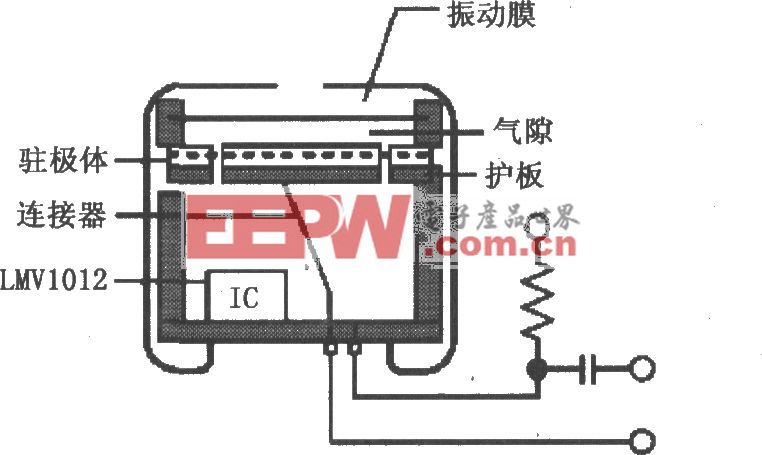

C8051F000单片机[1]是四边扁平贴片封装,内部集成了8通道的12位A/D转换器, 可编程增益放大器PGA,自带看门狗,具有32位数字I/O端口,体积小巧,集成度高,功耗较小,满足USB总线供电的要求。而且,C8051F000单片机最大工作频率可达到25MIPS,采用流水线结构,是单指令周期单片机,运行速度也较快,适于开发USB设备。

PDIUSBD12 是Philips 公司推出的符合USB1.1版规范的带并行总线的接口芯片。片内集成了320B的FIFO存储器,在批量模式和同步模式下均可实现1MB/s的数据传输速率,集成了模拟收发器,串行接口引擎,串行接口引擎实现了全部的USB协议层,包括并行/串行转换、位填充/解除填充、CRC校验/产生、地址识别和握手评估/产生等,从而减小了PDIUSBD12驱动程序开发的难度[2,3]。

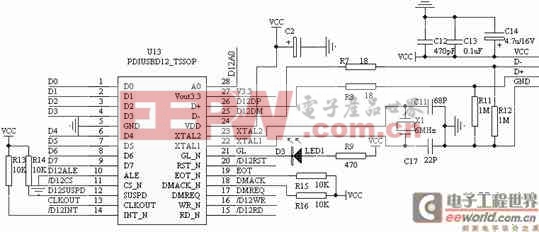

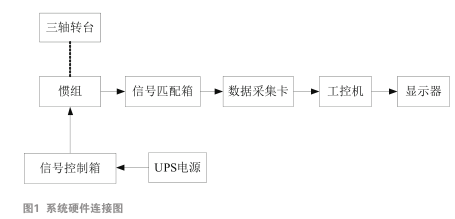

系统硬件包括主MCU、USB接口电路、模拟信号输入调理电路和电源转换电路等组成部分,其工作原理图如图1所示。

系统有8路模拟输入,模拟输入信号经过信号调理电路滤波、放大后送给C8051F000,此单片机自带的A/D转换器将输入的模拟信号转换为数字信号,并通过USB接口传送给计算机。计算机也可以通过USB接口向C8051F000发送命令。系统采用USB总线供电,由于USB总线只能提供+5V供电,而单片机C8051F000所需要的典型供电电压是3.3V,信号调理电路中的多路转换开关和运算放大器所需要的供电电压是+9V和-5V,故须设计电源转换电路将5V电压转换为3.3V、-5V和+9V,以便给相应的芯片提供电压。其中USB接口电路和信号调理电路的设计是最为重要的两个部分。

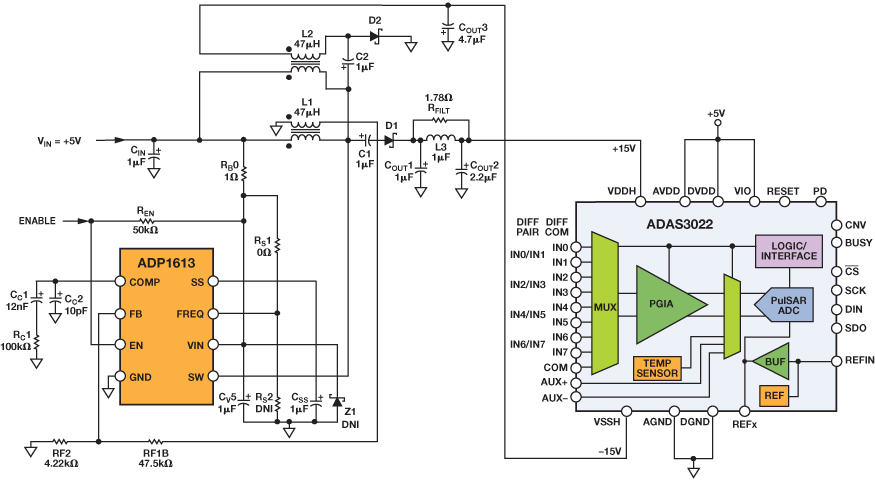

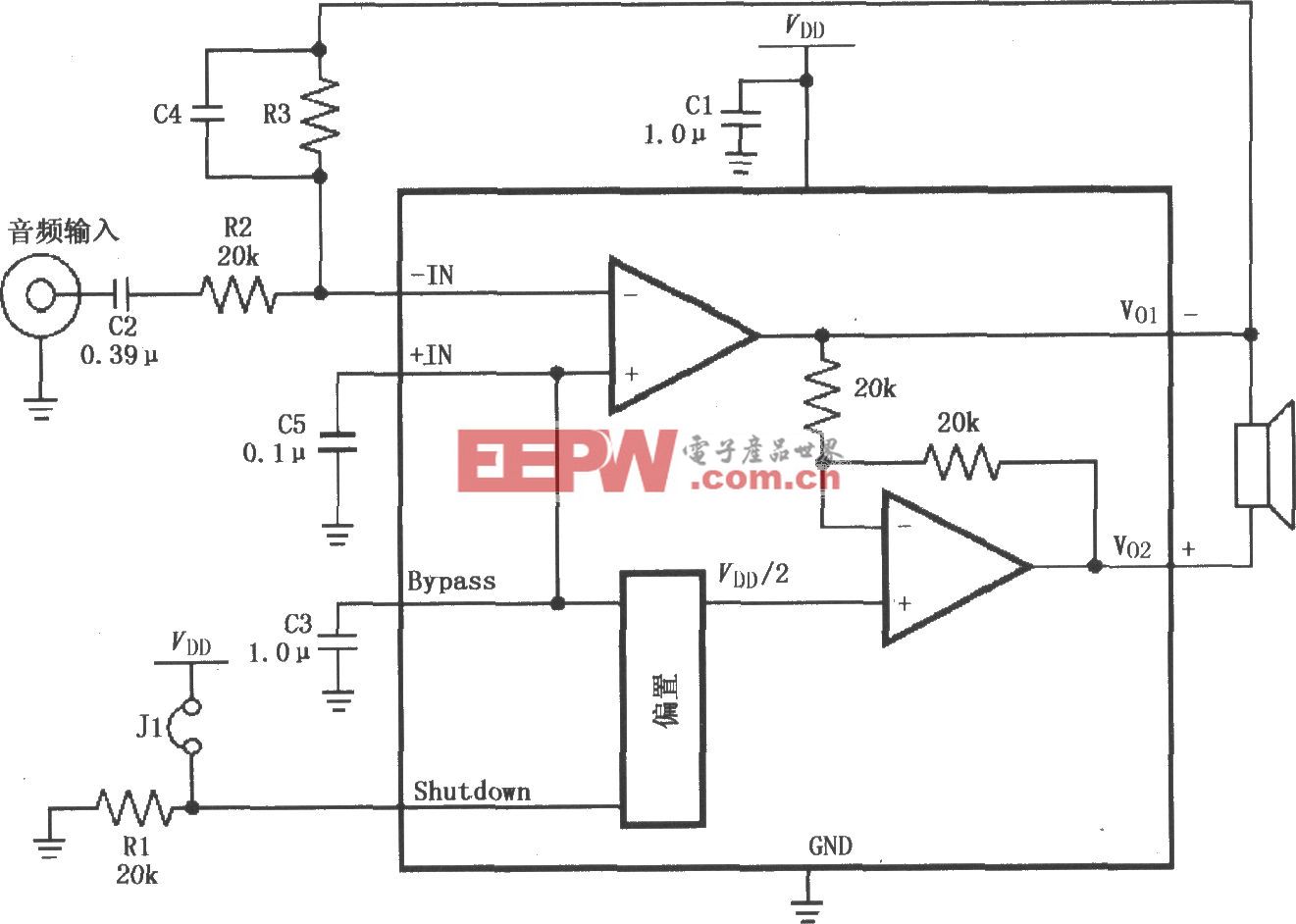

1.1 USB接口电路的设计

USB控制芯片PDIUSBD12与计算机及单片机之间的接口电路如图2所示。USB总线共4条线,两条电源线VCC和GND、两条差分数据线D+和D-。为了防止在读写数据的过程中电压波动,及附近大功率用电设备对电压的影响,在USB总线的两条电源线VCC和GND之间加了去耦电容。USB总线是采用差分数据传输,因此在任意时刻,只能有一个发送器或接收器。在D+/D-线上串接的两个18Ω电阻,及下拉的两个1M电阻是用来进行阻抗匹配的。

PDIUSBD12的8根数据线D0~D7与单片机的8根数据线分别连接,实现PDIUSBD12与单片机之间8位数据的并行传输,PDIUSBD12的读写引脚与单片机的I/O引脚相连,以实现单片机对PDIUSBD12的读写操作。PDIUSBD12的引脚A0是命令口和数据口的地址线,PDIUSBD12有两种数据总线方式:多路地址/数据总线和单地址数据总线,为了尽量少占用单片机的I/O引脚,系统采用单地址数据总线,PDIUSBD12的引脚ALE接地,引脚A0与单片机的I/O引脚相连,A0为1时,总线D0~D7上传输的是命令,A0为0时,总线D0~D7上传输的是数据。PDIUSBD12的挂起引脚SUSPD和中断引脚INT分别与单片机的一个I/O引脚相连,以实现PDIUSBD12挂起及PDIUSBD12向单片机发出中断。系统中PDIUSBD12的DMA功能没有使用,引脚DMACK和EOT都通过一个上拉电阻连到电源。振荡电路采用6MHz晶振,经过PDIUSBD12内部倍频电路之后,PDIUSBD12内部实际时钟为24MHz 。引脚GL通过一个绿色指示灯和一个电阻连到电源,当该仪器枚举成功以后,该指示灯亮,当计算机与该仪器进行通讯时,此指示灯闪烁。

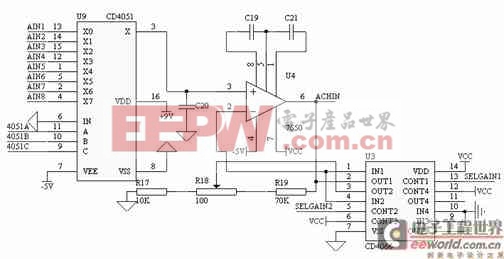

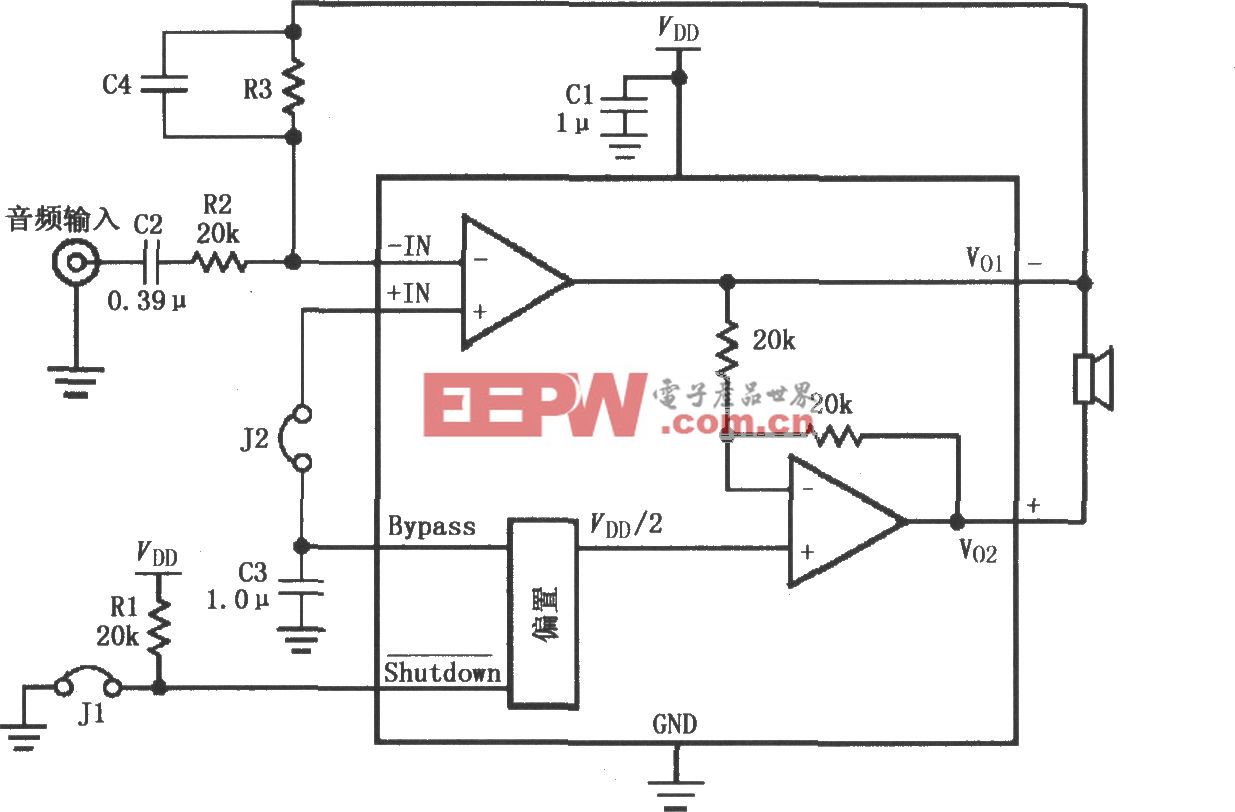

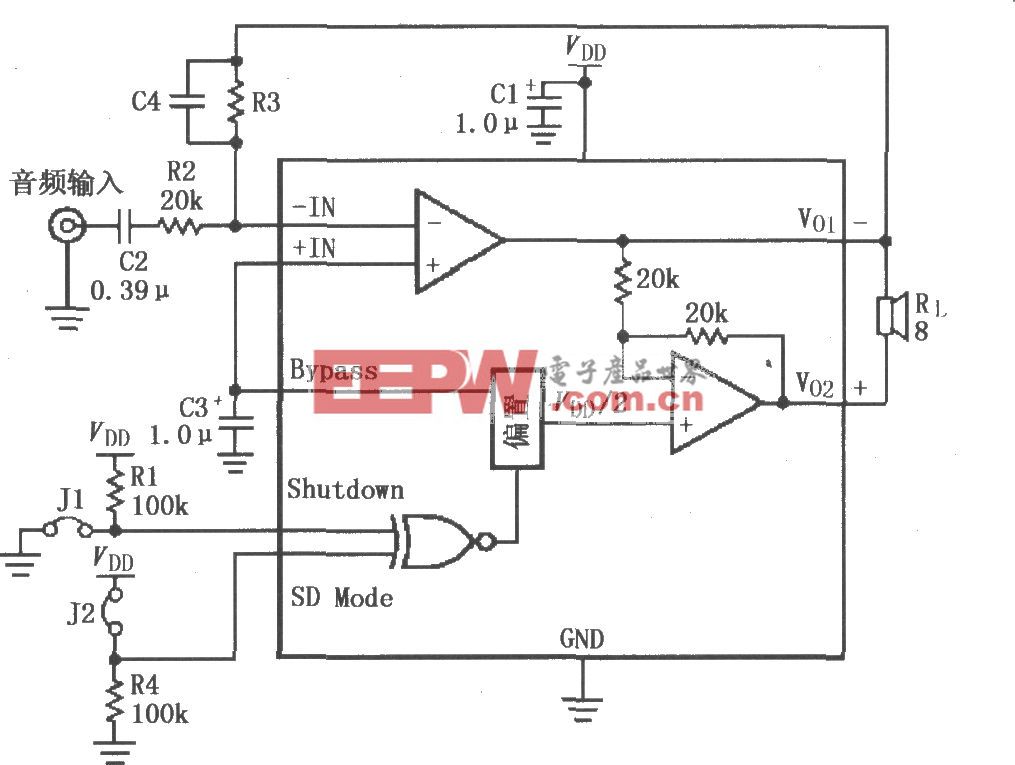

1.2 信号调理电路的设计

信号调理电路主要包括模拟信号多路选择、滤波和信号放大等组成部分,电路如图3所示。

系统电路设计中,只使用了单片机C8051F000本身自带的一路模拟输入AIN0;在单片机外围用多路模拟开关CD4051扩展了8路模拟输入。当单片机给CD4066的引脚CONT1输入一个低电平、给引脚CONT2输入一个高电平时,CD4066的引脚IN1和OUT1之间断开、引脚IN2和OUT2之间短接,运算放大器ICL7650的负端输入与它的输出断开,此时ICL7650对它的输入信号放大8倍;当单片机给CD4066的引脚CONT1输入一个高电平、引脚CONT2输入一个低电平时,CD4066的引脚IN1和OUT1之间短接、引脚IN2和OUT2之间断开,ICL7650的负端输入与它的输出直接短接,此时ICL7650和它的外围电路一起组成了一个电压跟随器,只是增大A/D转换器的输入阻抗,并不对它的输入信号进行增益放大。

C8051F000片内集成的增益放大器PGA编程范围为0.5~16,当ICL7650作为一个电压跟随器时,系统可编程增益范围为0.5~16;当ICL7650对输入信号进行8倍放大时,系统可编程增益范围为4~128,由此可见,系统可编程增益范围较宽,满足大多数情况下增益放大需要。

2 软件设计与实现

系统软件包括单片机固件程序,USB驱动程序及其链接库,及用户应用程序。为了降低开发难度及缩短开发周期,系统采用了周立功公司开发的D12 SMART套件中的USB驱动程序及其链接库[3],该链接库为用户应用程序提供了API函数,在编写应用程序时,只需调用API函数与采集系统之间交换数据,而不需要关心具体的USB通讯协议。

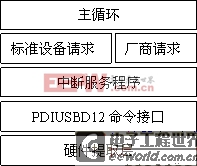

单片机固件设计采用中断驱动方式。CPU在前台进行数据采集, USB传输则在后台进行, 而其中断和主循环的数据交换则通过事件标志和数据缓冲区进行。这样既保证了数据采集的实时性,又获得了最佳的传输速率。固件结构如图4 所示。

中断服务程序主要负责从PDIUSBD12收集数据, 将建立包和OUT数据存入数据缓冲结构体,并设置相应的标志位;而主循环负责对数据进行处理,根据标志位区分是标准请求还是厂商请求,进而调用标准请求处理程序和厂商请求处理程序。其中标准请求处理程序主要负责在设备枚举过程中主机为识别设备而发送的请求, 主要包括读取USB设备描述符、给USB设备分配地址、配置USB设备等功能。只有在计算机与USB设备建立链接之后,计算机才能识别出USB设备,与USB设备进行通讯。而厂商请求处理中是自行定义的请求处理函数, 用来处理计算机发送给采集系统的各个设定命令,主要包括设定采集系统的量程、读取通道采样数据等命令。标准设备请求是在枚举过程中由安装在PC机中的USB驱动程序发送给USB设备的,而厂商请求是由用户应用程序通过调用USB链接库提供的API函数将命令传递到功能驱动程序后, 通过相应例程发送到USB设备的。

PDIUSBD12 命令接口是一套访问PDIUSBD12 所有功能的处理函数,主要包括对PDIUSBD12设置地址、设置端点使能、设置模式、读中断寄存器、选择端点、读端点状态、读取缓冲区、清缓冲区等操作。当固件中的其它程序需要对PDIUSBD12 进行操作时, 只须调用其中相应的子程序即可。

硬件提取层是固件中的最底层代码, 直接对PDIUSBD12访问,其执行与具体硬件电路有关,使用的单片机不同, 或者实现的设备功能不同时这部分代码也有所不同。

3 结束语

系统采用高速SOC单片机C8051F000和PDIUSBD12实现了宽量程的数据采集和基于USB接口的数据传输,基于该方案的采集系统已经在实验室调试通过,能够准确地进行数据采样和传输。本文作者创新点:利用了C8051F000片内集成的增益放大器PGA,并结合外围增益放大电路使系统的最大增益放大倍数达到了128倍,从而使系统能完成较宽范围内的电压信号采集;系统在PDIUSBD12与单片机之间的接口电路设计中采用了单地址数据总线方案,相对于通常所采用的多路地址/数据总线方式大大减少了单片机I/O引脚的占用。

评论