2.5Gb/s 0.35μm CMOS光接收机前置放大器设计

近年来,随着社会信息化程度不断提高,信息交换量呈爆炸性增长,光纤通信干线系统以其高速、大容量的优点被广泛应用于电信网、计算机网络。2.5 Gb/s超高速光纤通信系统已经投入使用。作为光纤通信系统中光接收机的关键部分,前置放大器的性能在很大程度上决定了整个光接收机的性能。

过去,对于高速的集成电路,多采用GaAs工艺来实现。但是随着深亚微米CMOS工艺的不断发展,栅长不断减小,现在0.35μm CMOS管的截止频率已经达到13.5 GHz,可以实现高速的集成电路。本文采用台湾TSMC0.35μmCMOS工艺实现了用于光纤传输系统STM- 16 (2.5Gb/s)速率级的前置放大器。

1 前置放大器简介

前置放大器在光接收机系统中所处位置如图1所示。由图1可见,光接收机主要由:光检测器、前置放大器、主放大器、数据判决电路、时钟恢复电路和分接器等电路组成。其中前置放大器处在光接收机系统的前端,处理的是微弱的信号,因此他的性能将直接影响整个光接收机的性能。

在接收机中,检测器感应光信号,输出μA级电流脉冲信号。而前置放大器的作用就是将此电流信号放大并转化成电压信号,主放大器将前置放大器输出的电压小信号放大至一个足够大且恒定的幅度,以便驱动后续时钟恢复和数据判决电路。时钟恢复和数据判决电路用来实现时钟和数据的再生。最后分接器把高速数据流分接为低速数据流。所以对前置放大器有以下几点要求:

(1)尽量减小电路本身引入的噪声。

(2)有足够高的增益,提高灵敏度。

(3)与信号速率相适应的带宽。

2 电路分析

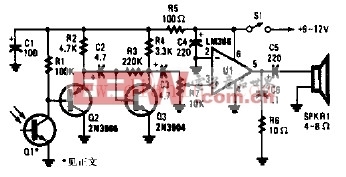

要把电流信号转化成电压信号,一种有效的方案是采用跨阻型前置放大器,如图2所示。

这种类型的放大器通过反馈电阻Rf提供负反馈,能提供一定的增益和大的带宽。

跨阻放大器的带宽表示为![]()

其中:RiRf/A为放大器的输入阻抗。

图2中A为放大器的开环增益;CT为输入寄生电容,包括光检测器的结电容和封装电容。所以,可以看出输入电阻和输入电容决定了放大器的带宽。例如,减小Rf,会使增益减小、带宽变宽。但Rf减小会使电路的噪声变大,降低放大器的灵敏度。因此,为达到电路的设计要求就需在噪声、增益和带宽等性能之间进行折衷。

3 电路设计

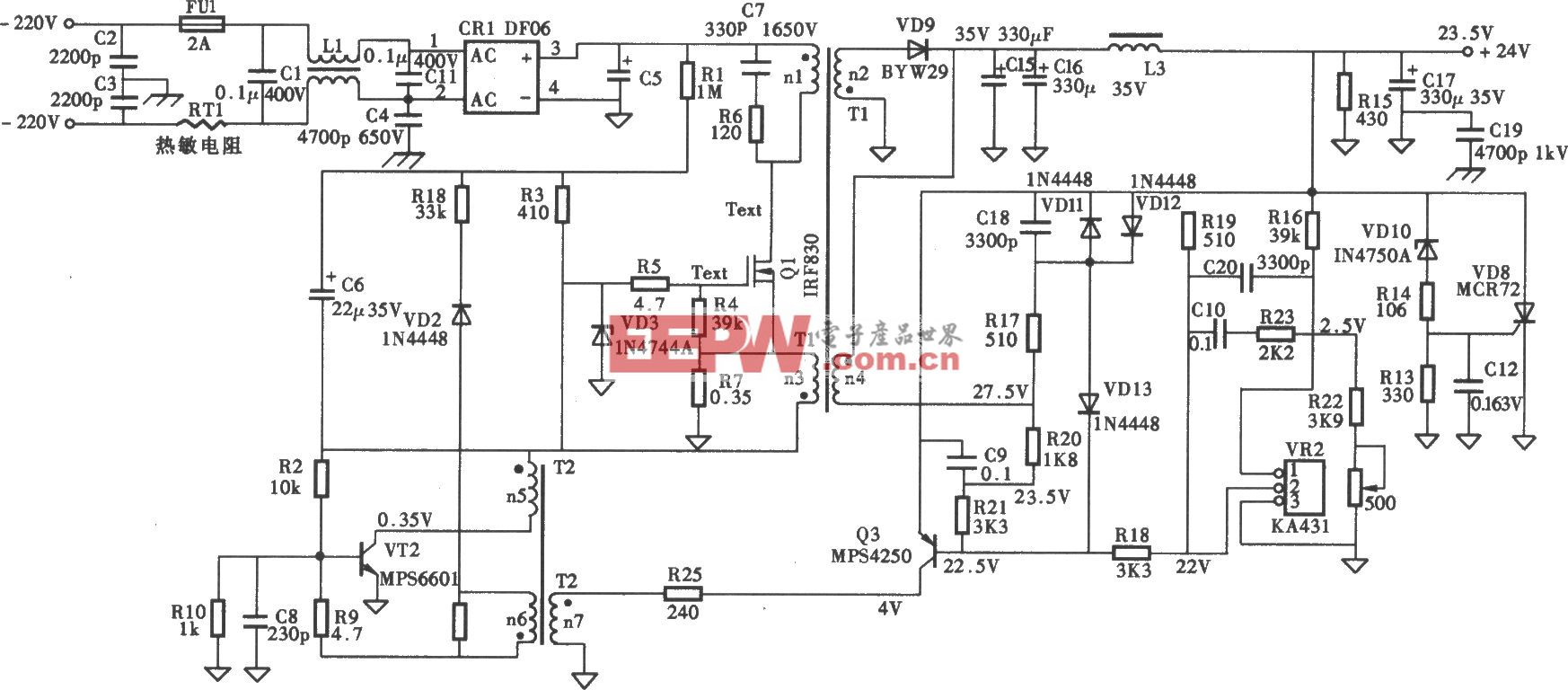

前置放大器的结构框图如图3所示。

图3中光检测器等效为电流源iin和电容Cin并联,Cin为结电容;另外,在前置放大器后增加了基本差分放大单元如图4所示,目的是实现电路的双端输出(其后主放大器为双端输入)并放大信号。采用两级差分放大器,之间用源极跟随器实现前一级输出和后一级输入的直流电平相匹配。

差分放大器的两输入端分别与跨阻放大器的输出端直接连接和通过一个RC滤波网络连接,从而保证基本差分放大器两输入端具有相同的直流电平。RC低通网络的RC常数决定了前置放大器的低频截止频率fL。在fL一定的情况下,R越大,所需要的C就越小。

跨阻放大器如图5所示,采用电压并联负反馈的形式。由共源放大和源极跟随组成基本放大部分,与Rf共同构成电压并联负反馈。

4 模拟结果

采用台湾TSMC0.35μmCMOS工艺提供的BSIM3元件模型和商用的SmartSpice电路仿真软件对前置放大器进行了仿真。

模拟交流分析得到的幅频特性曲线如图6所示。放大器总的增益为73 dBΩ,3 dB带宽为2.2 GHz。低频截止频率为50 kHz。

图7为输入5μA,2.5 Gb/s的伪随机序列,采用SmartSpice分析所得输出眼图。

5 版图设计

前置放大器核版图如图8所示,图中左上部分为跨阻放大器,是一个不对称的图形。右半部分是两级差分放大器,由于是对称的图形,所以在绘制版图时可以只画上边部分,然后复制翻转下来。跨阻放大器和差分放大器之间是RC低通网络的电阻,电容值比较大,采用外接形式。上下边界处图形为电源线,线的宽度要足够宽,以免电流过大烧毁。中间横线为地线,同时使用两层金属,这样既减小了线宽、节省了面积又能保证通过大的电流。

该版图采用Cadence设计工具设计。面积为40.15 mm×0.20 mm。该芯片已通过台湾TSMC0.35μm的N阱、两层多晶硅、四层金属的CMOS工艺流片,由于前置放大器和主放大器一同流片,芯片总面积为1 mm×0.70 mm。

芯片显微放大照片如图9所示,图中左半部分为前置放大电路,右半部分为限幅放大电路。

6 结果测试

由于测试条件所限,测试中只能用伪随机码发生器产生的电压脉冲信号来代替高速的脉冲电流信号,测试系统框图如图10所示。

图11为整个芯片在片测试结果。前置放大器输入为2.5 Gb/s峰峰值10 mV的电压信号,主放大器输出摆幅为200 mVp-p。

输出数据的眼图中心上偏约60 mV,这是因为测试采用单端输出。双端输出时无此现象。

7 结 语

本文介绍了采用0.35μmCMOS工艺实现用于SDH系统STM-16速率级光接收机的前置放大器的设计。电路模拟结果和对芯片测试结果令人满意,准备做印刷电路板对其进一步测试,并进行优化改进。

评论