简化电路设计的高通过率、高精度ADC-AD974

摘要:AD974是美国模拟器件公司生产的第一个200kSPS、4通道、16位数据采集系统。具有高通过率、低功耗、高精度等特性,此外,该器件还集成了外围器件,并采用串行通讯方式,因而可极大地简化数据采集电路的设计,非常适合于体积小、信号复杂的应用系统,如工业控制、医疗仪器等。本文介绍了AD974的特点,结构及应用设计。

AD974是一个四通道、16位串行通讯数据采集模数转换器。该器件内含模拟输入多路转换器、高速16位采样模数转换器和+2.5V参考电压。

1 内部结构及引脚

AD974的内部功能框图如图1所示。该芯片有28脚的DIP、SOIC和SSOP三种封装形式。引脚分布如图2所示。各引脚的功能说明见表1。

表1 AD974的主要引脚功能

| 引脚号 | 引脚号 | 功 能 说 明 |

| 1 | AGND1 | 模拟地。作为REF引脚的地参考点。 |

| 2-5, 25-28 | VxA VxB | 模拟输入范围选择端。 |

| 6 | BIP | 双极性偏移量。连接VxA输入以提供双极性的输入范围 |

| 7 | CAP | 参考缓冲输出。在CAP与模拟地之间连接一个2.2μF钽电解电容器 |

| 8 | REF | 参考输入/输出端。从该引脚可以获得+2.5V内部参考电压,也可以部参考电压代替内部参考电压。 |

| 9 | AGND2 | 模拟地 |

| 10 | R/C | 读取/转换输入端。用于控制转换和读模式。当CS为低时,在R/C的下降沿,AD974内部保持模拟输入并开始转换;在上升沿开始传送转换结果。 |

| 11 | VDIG | 数字电源端。通常为+5V |

| 12 | PWRD | 掉电模式输入端。若将它置于高电平,则禁止转换以达到降低电源消耗的目的,并把上一次的转换结果存储在片内移位寄存器中。 |

| 13 | EXT/INT | 数字时钟选择输入端,决定器件采用内部时钟还是外部时钟。 |

| 14 | DGND | 数字地 |

| 15 | SYNC | 数字输出帧同步端。只有在使用外部时钟时它才起作用。 |

| 16 | DATACLK | 串行数字时钟输入或输出端。 |

| 17 | DATA | 与DATACLK同步的串行数字输出端。转换结果存储在片内寄存器上。 |

| 18,19 | WR1 WR2 | 多路转换器写输入端。这些输入是通过内部或操作来产生混合多路转换器的使能输入,当WR1和WR2均为低电平时,将启动多路转换器。 |

| 20 | CS | 片选输入端 |

| 21 | BUSY | 忙状态信号输出端。 |

| 22,23 | A1,A0 | 通道选择端。见表2 |

| 24 | VABA | 模拟电源端。通常为+5V |

2 AD974的特性

表2 通道选择

| A1 | A0 | 通道 |

| 0 | 0 | AN1 |

| 0 | 1 | AN2 |

| 1 | 0 | AN3 |

| 1 | 1 | AN4 |

AD974具有如下的特点:

●支持复杂的信号采集系统。具有四个单端的模拟输入通道,能提供多种可设置的模拟输入范围,包括0V~4V、0V~5V或-10V~+10V;

●采用串行接口。与大多数微处理器的串行接口兼容,具有数据传送效率高、数据连线少的特点;

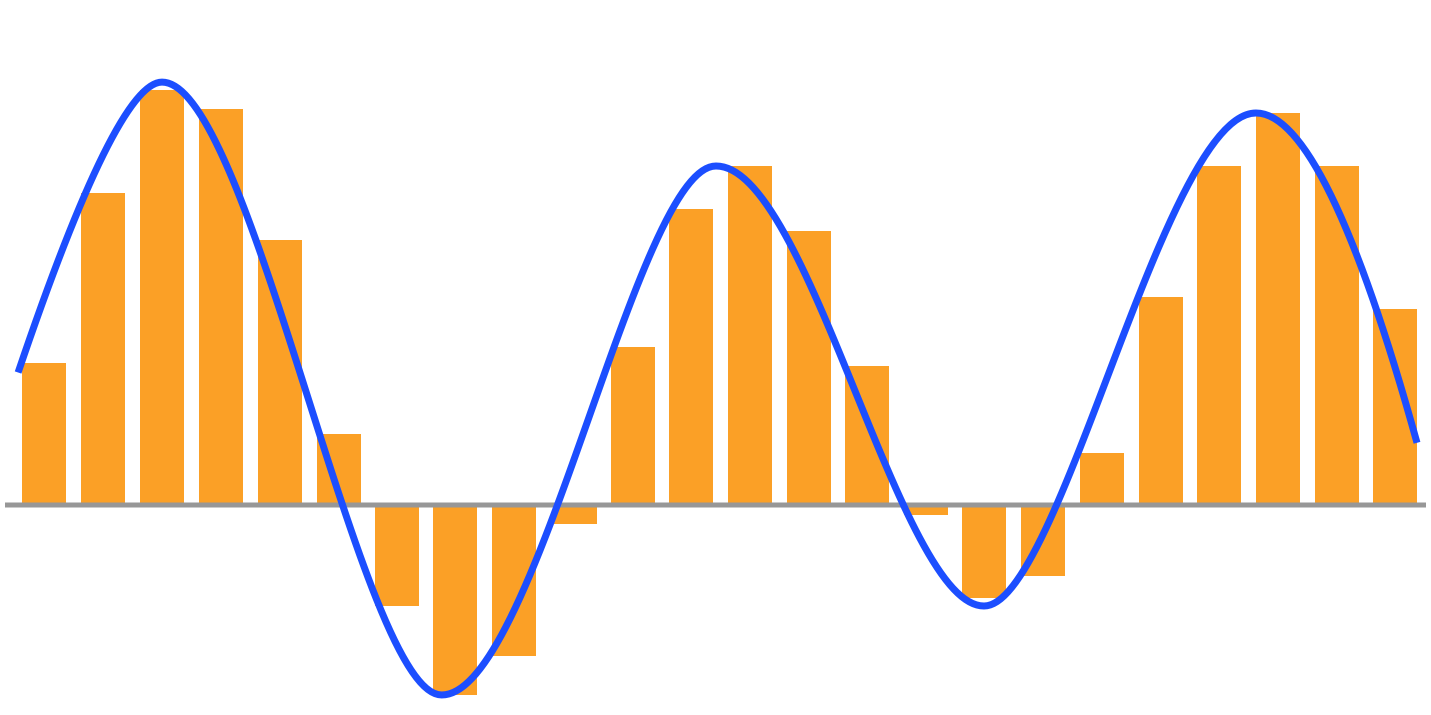

●能保证常规的直流参数,如偏移、增益和线性等;同时也明确给定了SNR(信噪比)和THD(总谐波失真)等交流参数;

●采用模拟器件公司先进的双CMOS(BiCMOS)工艺制造,该工艺能将高性能双极性器件与CMOS晶体管结合起来;

●可简化电路的设计,AD974由单电源+5V供电,并且只需较少的外围电路。为了达到简化电路设计的目的,AD974内部还集成了模拟输入多路转换器、高速逐次逼近开关电容ADC、时钟电路和内部2.5V参考电压电路等(参考电压也可以由外部参考电路供应);

●高通过率、低功耗。AD974可提供200kSPS的高通过率,而功率耗散最大却只有120mW,因此其转换速率可以高达2kSPS/mW。此外,在掉电模式下,AD974的功耗仅为50μW(典型值)。

3 应用设计

3.1 模拟输入

AD974可以工作在三种不同的满量程模拟输入范围,图3中的(a)、(b)、(c)分别给出的-10V~+10V、0V~5V和0V~4V时模拟输入与VXA、VXB之间的连接方式及额定输入阻抗。AD974具有两个模拟地(AGND1、AGND2)。而模拟输入是以AGND1引脚为参考的。

使用具有一定阻抗的模拟输入电路时,AD974可以由各种模拟放大器驱动。但为减小失真,非常有必要仔细选择驱动电路的运放。图4为AD974片内简化了模拟输入电路。

3.2 转换控制

AD974的模数转换由R/C、CS两信号来控制。在R/C降为低电平时,若CS也为低电平,在至嫠经过50ns后,输入信号将被保留在内部的电容阵列上并准备开始转换。一旦转换开始,BUSY信号将变为低电平直到转换完毕。图5给出了基本的转换时序图。在内部,信号R/C和CS需进行或操作,但是对啊一信信号先变为低电平做为开始转换的标志并没有严格要求。唯一的要求是这两个信号变为低电平的时间延迟不得少于10ns。转换完毕后,BUSY信号返回高电平,另一方面,AD974准备下一次转换以确保能继续跟踪输入信号。在某些情况下,将CS引脚保持低电平,而将R/C用于决定是开始转换还是读取数据。需要指出的是,在AD974上电后进行首次转换时,其DATA输出将是不确定的,转换输出需要经过一定时间之后才能稳定下来。模数转换可以使用由AD974的内部时钟,也可以使用外部时钟,这并不影响转换结果的连续性。如果EXT/INT为低电平,则AD974被设置为内部数据移位时钟模式;相反,如果EXT/INT为高电平,则AD974被设置为外部数据移位时钟模式。

4 应用举例

利用AD974与微处理器的接口电路可以很方便地测量传统的直流信号,如果与数字信号处理器接口,则更适合于交流信号的处理。AD974了容易与绝大多数微处理器的串行或I/O端口连接。适当使用外部缓冲可以避免数字噪声进行模数转换器中。

4.1 与SPI的接口

图6是AD974与带串行外围接口(SPI)的微控制器的接品电路框图。该接口电路采用外部时钟模式(EXT/INT=1),转换脉冲来自于微控制器,AD974在该系统中做为从设备。转换脉冲的初始化可以通过响应内部时钟中断而进行。输出数据的读取可以根据转换信号的结束标志(变为高电平)来初始化。

4.2 与ADSP2181的接口电路

图7是AD974与ADSP2181数字信号处理器的接口电路框图。在该数字采集信号系统中,AD974采用内部时钟模式(EXT/INT=0),转换命令由外部振荡器提供。对于ADSP2181,SPORT可以看作非连续时钟,为了使SPORT时钟与外部非连续时钟保持同步,在数据读取操作的准备阶段必须采取以下步骤:

(1)通过系统控制寄存器,启用SPORT0;

(2)将SCLK分频寄存器置0;

(3)通过将PFTYTE中与PF0和PF1的对应位分别置0和1而将PF0和PF1设置为输出端口;

(4)通过PF0将RFS0置为低电平。然后通过程序把接收帧同步脉冲设置为高电平有效;

(5)通过PF1将CS置为低电闰,启动AD974进行转换;

(6)通过IMASK寄存器启用SPORT0接收中断;

(7)等待至少一个以上的转换周期,忽略被接收的数据;

(8)通过PF1将CS置为高电平,禁止AD974进行转换;

(9)等待大约一个转换周期;

(10)通过PF0将RFS0置为高电平;

(11)通过PF1将CS置为低电平,启动AD974进行转换。

这样,在随后的转换过程中,ADSP2181的SPORT0就会与外部非连续时钟保持同步。

5 结束语

AD974是一款新颖的高精度、高速模数转换器,它在设计上的许多特性可为用户的使用带来极大便利。AD974适合于大多数数字信号采集系统。随着该产品的推广,相信它在工业控制、医疗仪器等方面的应用交更加普遍。

评论