流水线型ADCMAX1200及其与DSP的接口

摘要:新型的流水线结构模数转换技术是实现高速、高精度、低功耗的数据转换的新技术。介绍16位MAX1200的结构、原理及其在高速数据采集系统中与DSP的接口及应用,可对流水线型ADC有实频了解。

1 概述

为了适应计算机、通信和多媒体技术的飞速发展以及高新技术领域的数字化进程不断加快,ADC在工艺、结构、性能上都有了很大进步,正在朝着低功耗、高速、高分辨率的方向发展。新型的流水线结构是实现高速低功耗ADC的新型有效的方法。MAX1200就是采用这一新技术的高速、高精度、低功耗ADC的代表。

*单电源+5V供电;

*±VREF差分输入,正向参考电压RFPF由外部+4.906V电压基准提供,负向参考电压RFNF接至模拟地;

*输入信号fin=100kHz时,非杂散动态范围为91dB;

*1Msps,+5V供电时功耗273mW;

*±0.5LSB差分非线性误差;

*三态、二进制补码输出;

*快速、可控自校准功能;

*44脚MQFP封装。

表1为引脚说明

表1 引脚说明

| 引脚号 | 引脚名称 | 说 明 |

| 1 | ST_CAL | 自校准触发数字输入端 ST_CAL=0,正常转换;ST_CAL=1,启动自校准功能 |

| 2、4、5 | AGND | 模拟地 |

| 3、6 | AVDD | 模拟电源+5(1±0.05)V |

| 7 | DOR | 数据溢出位 |

| 815 | D15D8 | 输出数据高8位 |

| 16 | DRVDD | 驱动输出的数字电源,+3~+5.25V,必须保证DRVDD≤DVDD |

| 17、28、29 | DGND | 数字地 |

| 18~25 | D7D0 | 输出数据低8位 |

| 26 | TEST1 | 测试1脚,不接 |

| 27、30 | DVDD | 数字电源,+3~+2.25V |

| 31 | CLK | 输入时钟,AVDD获取能量可避免抖动 |

| 32 | DAV | 数据有效时钟,通过此时钟控制,数据可传送到存储器或其它任何数据接收系统 |

| 33 | OE | 输出使能 0E=0,D0~D15为高阻态;OE=1,D0~D15使能 |

| 34 | TEST0 | 测试0脚 |

| 35 | CM | 普通模式电压。模拟输入,用来驱动介于正负参考电压的中间值 |

| 36 | RFPF | 正参考电压,强制输入 |

| 37 | RFPS | 正参考电压,敏感输入 |

| 38 | RFNF | 负输入电压,强制输入 |

| 39 | FPNS | 负参考电压,敏感输入 |

| 40 | INP | 正输入端 |

| 41、42 | NC | 不接 |

| 43 | INN | 负输入端 |

| 44 | END_CAL | 校准结束标志位 END_CAL=0,校准正在=1,正常转换 |

2 工作原理

流水线型(pipeline)ADC又称为子区式ADC,由级联的若干级电路组成。每一级包括1采样/保持放大器,1个低分辨率持ADC和DAC,以及1个求和电路,其中求和电路包括可提供增益的级间放大器。快速精确的n位转换器分为两段以上的子区(流水线)来完成。每级电路的采样/保持器对输入信号取样后,先由1个m位分辨率的粗A/D转换器对输入进行量,接着用1个至少n位精度的乘积型数模转换器(MDAC)产生1个对应于量化结果的模拟电平送至求和电路,求和电路从输入信号中减掉此模拟电平,并将差值精确放大某一固定增益后送交下一级电路处理。经过各级这样的处理后,最后由1个较高精度的k位细A/D转换器对残余信号进行转换。将上述各级粗、细A/D的输出组合起来构成高精度的n位输出;同时必须满足以下不等式,以便纠正重叠错误:

l·m+k>n

其中,l为级数,m为各级中ADC的粗分辨率,k为精细ADC的细分辨率,而n是流水线ADC的总分辨率。图1所示为MAX1200的4级流水线ADC的原理图及每级内部结构图。

图1中m=8,l=4,n=16。由于采用的开关电容流水线结构中存在开关电容之间的失配问题,所以整个电路的精度由校正和校准逻辑控制。流水线结构的4个采样过程在输入信号被采样和数据输出到D15~D0之间引入的等待时间,也就是流水线的延迟时间;但是,在连续采样的情况下可以获得连续的输出,只是输出数据是前面的采样输出。时序如图2所示。

总地来说,流水线ADC不但简化了电路设计,还具有如下优点:

①每一级的冗余位优化了重叠误差的纠正,具有良好的线性和低失调;

②每一级具有独立的采样/保持放大器,前一级电路的采样/保持可以释放出来用于处理下一次采样,因此,允许流水线各级同时对多个采样进行处理,从而提高了信号的处理速度,典型的为Tconv100ns。

③功耗低;

④很少有比较器进入亚稳态,从根本上消除了火花码和气泡,从而大大减少了ADC的误差;

⑤多级转换提高了ADC的分辨率。

(1)输入模拟信号

全差分的开关电容电路(SC)用来控制参考电压和模拟输入,如图3所示。采用差分输入信号比单端输入具有更好的THD和SFDR性能,并且具有两倍的信号量程、普通模式下的抗干扰性提高、有效地消除偶次谐波、对输入信号的放大器预处理要求不高等优点。如果使用单端输入,负输入引脚INN连接到普通模式电压引脚CM上,输入模拟信号接正输入端INP。为了充分利用ADC的直到奈奎斯特频率的优良的AC特性,应尽量采用差分输入方式。可以通过电路转换将单端输入转换成差分输入。如图4所示,利用低噪声、宽带的运算放大器MAX4108可以保证MAX1200输入信号在全功率带宽范围的信号纯净。为提高信噪比减小信号失真,在输入信号进入ADC之前,可采用低通或带通滤波器调理输入信号。通常对于低频输入信号(100kHz)可采用有源滤波器,高频输入信号则采用无源滤波器。

(2)参考电压

选择低噪声的参考电压可以提高良好的负载稳定性和低的温度漂移。MAX1200的参考电压驱动大约1kΩ的片上电阻和21pF的开关电容。为了满足动态特性的要求,参考电压要在一个时钟周期内稳定在0.0015%,因而要设计恰当的驱动电路,如图5所示。参考电压也可采用单端输入或图3所示的差分输入,参考电压不可高于模拟电压AVDD或低于地。参考电压引脚处的电容用来提供每一时钟周期内的动态电荷,这些电容必须具有低的电解质吸收性能;运算放大器MAX410可以保证参考信号的精度。通常典型的正参考电压RFPF可由4.096V的驱动电压基准(如MAX6341)提供,负参考电压可直接和模拟地相连,这样可达到最佳的信噪比。如果系统对THD性能的要求比SNR更为重要,那么可选择差分电压VRFPS=+3.5V,VRENS=+1.5V。普通模式电压引脚CM对ADC的性能影响很大,采用VCM=(VRFPS+VRFNS)/2,可以保证有很好的动态性能。图5所示VCM可采用分压得到。

(3)时钟

流水线型ADC通常需要50%占空比的时钟,MAX1200采用图6所示的电路来产生所需的时钟。

在这里,时钟发生器与信号源要有匹配的频率范围、振幅、压摆率。如果输入信号的压摆率很小,那么,时钟抖动可以忽略;如果信号的压摆率很高,则时钟的抖动应该限制到最小。因为,对于全振幅输入的正弦波可能达到的最大信噪比取决于时钟的抖动:

采用图6所示的低噪声和低相位噪声的信号发生器,可以获取需要的时钟。

(4)校标功能

流水线操作采用低分辨率的乘积型数模转换器(MDAC),其内部的开关电容存在失配问题,因而MAX1200的精度受限于MDAC的精度。MAX1200具有自校准功能,可将电容之间的失配情况进行计算并存储在片上存储器中,以便应用于对输入信号的校准中。在校准过程中,首先,时钟必须连接工作,ST_CAL由一最小宽度为4倍时钟周期但不超过17 400个时钟周期的正脉冲触发,可与时钟开行输入。当ST_CAL触发1~2个时钟周期后,END_CAL变为低电平并保持到校准结束。在这一期间参考电压必须保持稳定在0.01%,否则校准是无效的。在校准过程中,模拟输入INP和INN一般不接入信号,但如果接入静态输入可以获得更好的校准性能。一旦END_CAL变高则意味着校准结束,此时ADC进入模数转换状态。具体时序如图7的慰。校准结束后,MAX1200对电源±5%的变化或温度的变化都不敏感,但当温度变化超过±20℃时则需要重新校准。

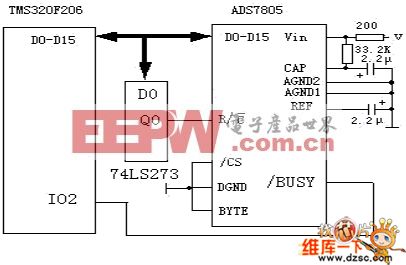

3 MAX1200与DSP的接口

这里,采用美国TI公司的TMS320F206(以下简答F206)。F206是一种低价格、高性能16位定点DSP,目前已广泛应用于图形图像处理、语音处理、仪器仪表、通信、多媒体及军事等领域。F206运算速度较快(可达40MIPS),功能较强,源代码与'C1x、'C2x兼容,且与'5x向上兼容,片内外设向TMS320C5x靠拢。其内部采用程序和数据分开的哈佛结构,具专门的硬件乘法器,采用了四级流水线操作,提供了特殊的DSP指令,可以快速实现各种处理算法。图8为MAX1200的外围电路及与F206的接口电路。

下面给出应用DSP进行ADC数据采集的程序:

.title "MAX1200 ADC";标题

.copy "init.h" ;变量和寄存器定义

.copy "vector.h" ;矢量标号定义

.text ;代码段

F206系统初始化

start:clrc cnf ;映射块B0到数据存储区

ldp #0h ;页指针设置为0

setc intm ;关中断

splk #0000h,60h

out 60h,wsgr ;设置0等待周期

*设置中断*

splk #0ffffh,ifr ;中断标志复位

splk #0001h,imr ;设置INT1中断有效

splk #0010h,60h

out 60h,icr ;设置中断模式

*设置IO口输入输出状态*

splk #0c004h,60h ;设置IO2为输出,IO3为输入

out 60h,aspcr

*设置从ADC的接收数据存放位置及数据长度*

lar ar1,#rxbuf ;接收数据从0300h单元开始存放

lar ar0,#size ;接收数据长度0020h个数据

mar *,ar1 ;设置AR1为当前辅助寄存器

*控制ADC的OE,启动自动校准,等待校准完毕后接收数据*

splk #00f4h,61h

out 61h,iosr ;设置ST_CAL=,启动ADC自动校准

in 62h,iosr ;等待自动校准完毕

bit 62h,8

wait:bcnd wait,ntc ;自动校准正在进行

clrc tc ;自动校准完毕,清除TC

clrc intm ;打开总中断

loop:idle

b loop;

*INT1中断服务程序——接收、存储数据*

inpt1:in *+,000h ;接收数据并存储到辅助寄存;器所指示数据存储单元

mar *,ar0

banz skip,ar1

lar ar1,#rxbuf

lar aro,#size

skip:clrc intm

ret

.end ;程序结束

4 小结

利用流水线型ADC可以实现高速精度的模数转换,这一技术是新型ADC的代表。MAX1200的原理特性及其与DSP的配合使用,可将高速、高精度、低功耗的数字采集系统广泛地应用于数字通信、高分辨率图像系统、扫描仪等各种数字化系统中。

评论