图像叠加及控制电路

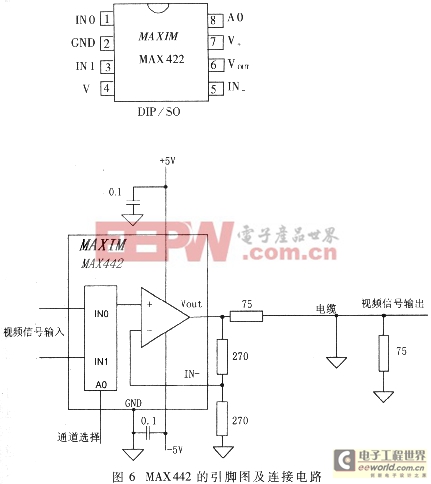

MAX442的引脚图与连接电路如图6所示,图中的电容容值单位为μF,电阻单位为Ω。INO,IN1为两路视频信号的输入端,分别外接现场视频信号和黑电平;地址线AO控制“二选一”开关,选择输出哪个通道的信号。AO在屏幕编辑缓冲区中仅占一位空间,所以叠加控制字可以按位读写修改,这大大减少了所需的屏幕编辑缓冲区RAM的存储空间。在RAM中数据是按照字节存取的,因此在输出时,需要把从RAM中读出的数据进行并串转换,送到MAX442的AO端。这种“八选一”的数字逻辑电路用可编程芯片GAL可以很方便地实现,成本也不高,因此我们选择用GAL实现,逻辑表达式从略。

屏幕编辑缓冲区的控制设计

屏幕编辑缓冲区选择用RAM,是因为用户要求叠加的均是规则的几何图形,由CPU 90C32动态计算图形各点的位置算法非常简单;用户完全可以接受。

CPU和视频输出端都要对屏幕编辑缓冲区进行访问,其中CPU要完成对RAM的刷新,即“写”RAM;输出端仅需读RAM。也就是说,对RAM的访问可以定为“写时禁止读”,“读时禁止写”。让它们共用数据总线DB和地址总线AB,而通过控制CPU和行场计数器的地址锁存器的使能端E,来分时使用。可见,这两组地址锁存缓冲器的使能端E是互斥的,可以仅用90C32的一根PI端口I/O线来作一个“单刀双掷开关”,由CPU通过控制这根I/O线来实现总线的分时使用。所以在电路设计中,RAM的片选端CS直接接地,写使能端WR与CPU的WR相连,而读使能端OE与行/场计数器的地址锁存器的使能端E相连。当CPU要对屏幕编辑缓冲区写时,选通它的地址锁存器的使能端E,同时行场计数器的地址锁存器被禁止,RAM的读使能端也被禁止,即RAM处于“只写”状态。反之,当CPU不需要对RAM刷新时,选通行/场计数器的地址锁存器的使能端E,同时RAM的读使能也被选通,RAM处于“读”状态,并且禁止写操作。用这种“存储器双总线技术”,避免了对屏幕编辑缓冲区的冲突访问,从而保证数据的完整性,得到稳定、正确的叠加视频图像。

CPU 90C32的典型扩展电路包括程序存储区的扩展、数据存储区的扩展、时钟电路和晶振电路的扩展。考虑到项目需求并保留一定的扩充余地,存储器ROM选用27256芯片,RAM选用61256芯片。其中除RAM(屏幕编辑缓冲区)为临界区,需要特殊设计以外,其它电路与通用的单片机扩展电路完全相同,在此不另做介绍。

2.4 按键译码电路

本项目中,用户在人机交互选择叠加光标的形状与大小时,仅需要四个按键,因此不必使用功能强大的8279芯片,直接扩展90C32即可。四个按键经过译码,送到90C32的P1端口,这个译码逻辑非常简单,同样用GAL实现,逻辑表达式从略。在实际使用中,用户选择一次光标的大小与形状之后,总会稳定一段时间去进行其主要工作,所以操作按键的时间对于整个系统的工作时间而言是很短的。CPU对按键的响应采用中断方式,这可以比轮询方式大大减少对CPU处理器资源的占用。在按键电路中,一共占用P1端口2根I/O线,AO、A1是译码后的按键地址(或代码);另有INT是检测是否有按键被按下的中断信号线,它与90C32的外接中断输入端 相连接。通常INT为高电平,若有按键被按下,INT为低电平,CPU可响应中断。

相连接。通常INT为高电平,若有按键被按下,INT为低电平,CPU可响应中断。

按键电路的设计,也选择简单、典型而可靠的通用电路实现。目前,按键是利用机械触点的合与断来作用的,当电信号通过按键时,在闭合及断开的瞬间均有抖动过程,会出现一系列的负脉冲,持续时间一般为5~10ms。按键的稳定闭合期,由操作人员的按键动作所决定,一般为十分之几秒至几秒时间。为了保证CPU对按键的一次闭合,仅做一次键输入处理,必须去除抖动影响。通常去抖影响的措施有硬、软件两种,本项目用两重 去抖来提高可靠性:硬件设计中,为每个按键在输入端加一个一端接地的电容,滤去毛刺脉冲;软件设计中,有按键去抖过程,具体思想在软件设计中详细讲述。

评论