新型高度集成化的视频字符叠加系统的研究

视频字符及时间叠加器是在视频信号中混入字符或时间信号,从而在屏幕的特定位置上与图像信号同时进行显示的设备。这项技术是应用电视技术中的一个重要领域,在应用电视系统中发挥着重要的作用。从视频字符叠加器的工作方式及本身电路的构成来看,到目前为止已有三种不同的实现方案。

第一种方案是通用中小规模集成电路实现方案。即,全部采用逻辑门,计数器,移位寄存器等通用中小规模集成电路实现单路规模字符集时间叠加。

第二种方案是基于FPGA的多路实现方案。即,在共用字库ROM,一片CPU和实时时钟的前提下,利用FPGA集成若干路显示RAM计数的、独立的扫描电路,实现多路字符叠加。

第三种方案是主控机加显示执行机实现方案。可采用ATMEL 8951单片机作主控机,若干片AT90S1200单片机作为显示执行机,利用AT90S1200的I/O口管脚自定义一种串行通讯协议,实现多路字符叠加。

其中,第一种方案只适用于单路设计,随着专用芯片和单片机技术的发展,这种方案会逐渐被淘汰。第二种方案原理与第一种类似,利用可编程逻辑器件使电路简化不少,但该方案的成本较高。第三种方案利用软件实现了硬件扫描电路的功能,比较灵活,成本较低,但是只适用于显示字符相对较少的场合,若显示字符很多,软件就过于复杂,很难保证连续显示。

近年来,视频监控系统的广泛应用使其容量不断扩大,因此,它的显示编辑功能、可靠性及电路的规模和复杂程度也就成为设计者十分关注的一个问题。为了保证在系统容量较大的情况下,实现低成本、高性能的字符叠加,文章尝试使用了高度集成化的字符叠加系统,其中采用了Microchip公司推出的单片机PIC16C73和NEC公司推出的专用字符叠加芯片uPD6453。

2 新型的汉字字符叠加系统

文章中的汉字字符叠加系统是一个四路同时采样的字符叠加系统,采用一片PIC16C73微处理器和四片uPD6453芯片,对四路模拟视频输入信号分别进行字符叠加,进而产生四路字符与视频信号叠加的混合信号并输出到终端设备。其基本工作原理是:首先,通过同步信号分离模块将外输入的视频信号中的行场同步信号分离出来,该分离信号引入uPD6453,由PIC16C73向uPD6453发送控制命令,如显示控制、字符RAM写地址控制等,对四路uPD6453循环操作,按照系统功能需要产生相应的字符,与外输入视频信号进行叠加得到混合信号输出到终端设备显示。

2.1 字符叠加系统硬件电路设计

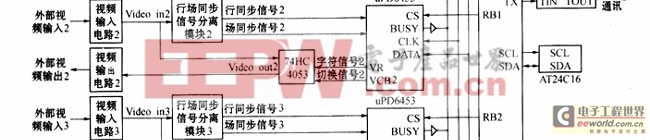

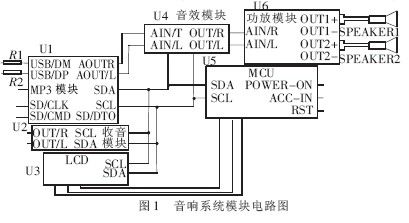

这里采用PIC16C73和uPD6453进行汉字字符叠加,其硬件结构框图如图1所示。

该硬件结构由以下8个部分组成:

2.1.1 视频输入电路

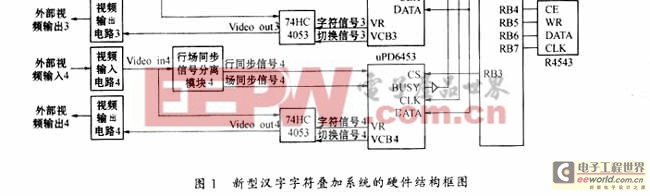

由于外部视频输入信号的基线为0V左右,要与由uPD6453芯片生成的字符信号进行叠加,必须提升基线值到2V左右,其设计电路如图2所示。该电路输出信号Video in与外部视频输入信号相比较,只是基 线不同,二者波形形状完全一致。

2.1.2 行场同步分离模块

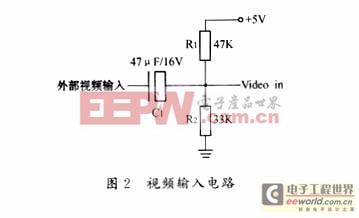

又称视频同步信号提取电路。现在市场上已有不少可实现行场同步信号分离的专用集成电路,如LM1881等,但成本较高。文章使用分立模拟元件设计该电路,性能十分稳定可靠,同时大大降低了成本,其设计电路如图3所示。

2.1.3 字符生成模块

如图1所示,四片uPD6453芯片的CS端分别与PIC16C73的RB0,RB1,RB2,RB3相连接;四片uPD6453芯片的BUSY端口共用,与PIC16C73的RC1端口连接;四片uPD6453芯片的CLK端口共用,与PIC16C73的RC3端口连接;四片uPD6453芯片的DATA端口共用,与PIC16C73的RC5端口连接。微处理器PIC16C73对uPD6453进行各种控制命令的操作,产生的字符包括汉字,字母和数字。有关PIC16C73的端口功能和uPD6453的控制命令及控制时序详见NEC公司的数据手册,这里不再讲述。这里需要说明的是,uPD6453显示的字符大小有时不符合要求,我们注意到uPD6453外接的电感电容振荡电路对显示字符的横向长度影响很大,但芯片手册上并未给出具体的参数值,经过反复试验,我们认为,电感取15μH,电容取56pF比较合适。若稍微调整电感值,则可改变显示字符横向尺寸,使用时可根据自己的需要选用。

2.1.4 时钟模块

本设计中加入一片时钟芯片R4543,该芯片采用内置晶振,精度比一般的时钟芯片高。R4543与CPU的连接如图1所示,R4543的信号端CS,WR,DATA,CLK分别与PIC16C73的RB4,RB5,RB6,RB7相连接,时钟芯片R4543的读写时序可参见其用户手册,这里不再讲述。微处理器PIC16C73对R4543可进行读写操作,通过uPD6453在视频图像信号上叠加当前时间,调整校对当前时间。

2.1.5 汉字字库模块

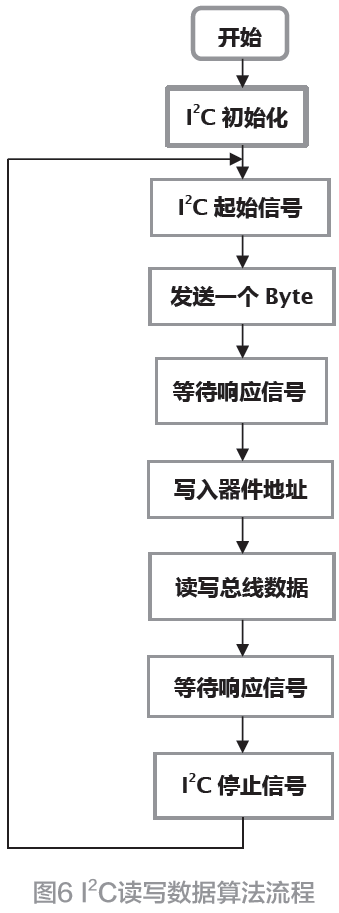

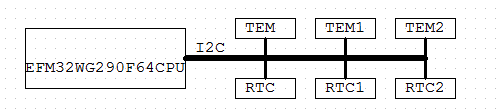

由于uPD6453中固化的字模主要是日文字符,没有所需要的汉字。但它有16个空的RAM区,可以供用户任意填写(详见NEC公司的数据手册),因此,系统需要能够存储汉字点阵的字模芯片,其容量大小取决于系统显示汉字的范围。文章采用ATMEL公司生产的AT24C16作为字模芯片,该芯片容量为2Kbyte,用于存储12×12点阵的字库数据,AT24C16的数据存取方式是I2C串行方式。如图1所示,AT24C16的SCL和SDA端口分别与PIC16C73的I2C功能口RC3(SCL)和RC4(SDA)连接,外接10 kΩ上拉电阻,可实现I2C串行读写操作。PIC16C73通过I2C总线读取字模芯片中的汉字点阵数据,再写入uPD6453片内RAM区,有关I2C总线的读写时序详见参考文献2。

2.1.6 串行通信模块

如图1所示,微处理器PIC16C73的RX(RC6)和TX(RC7)端与MAX202的ROUT和TIN端口相连接。PIC16C73具有完善的串行通信接口SCI,利用RX和TX两个引脚作为通讯线的二线制串行通信接口,可将其定义为全双工异步方式。再通过外接一片MAX202芯片将TTL电平转化为RS232标准电平,可以实现远距离传输与上位机通讯。由上位机下传12×12汉字点阵数据和当前时间数据,可实现AT24C16中字模点阵数据的更新并可下传当前时间数据,与时钟芯片时间相对比以校对调整时间。

2.1.7 字符与视频信号叠加电路

该模块主要通过74HC4053芯片来实现字符信号与视频信号的叠加。电路如图1所示,视频输入信号Video in和字符信号分别接入74HC4053的两路通道,切换信号为uPD6453产生的输出信号VCB,它与74HC4053的通道切换端相连接。其工作原理为:通过切换通道的方法,在要显示字符的时候,切换到字符信号通道,其余时候选通Video in通道,74HC4053产生的输出信号Video out为视频信号与字符信号的叠加信号。

2.1.8 视频输出电路

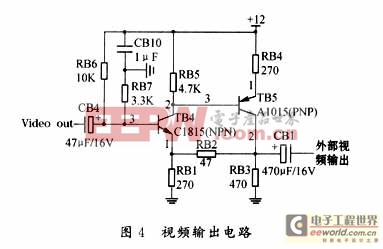

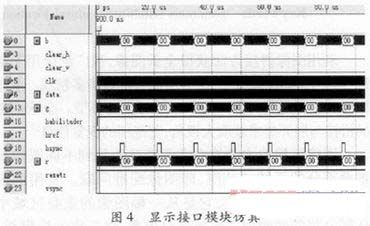

图1中,由74HC4053输出的字符与视频混合信号Video out不能直接输出到外部终端设备,必须对其进行处理,将基线为2V左右的混合信号还原成基线为0V左右的视频输出信号。图4给出了一种视频输出电路的设计。

2.2 字符叠加系统的软件设计

一般而言,需要在视频图像信号上叠加标题和时间信息,以使将来对录像存档的图像信号进行分辨和查找,这是字符叠加系统应完成的功能。同时,为了使叠加的字符信息不影响正常的图像显示,字符的显示位置也应是可调整的,基于这两点,将整个系统的软件设计分为6种状态,其状态图如图5所示。

2.2.1 修改时间

该设置有“修改”和“不修改”两种状态,若为“修改”状态,则按下存储键后,系统时间将被更新,否则,系统时间保持不变。

2.2.2 字幕种类选择

通过该设置可以切换字幕显示的类型,例如显示年月日,隐含年月日,显示当前时间,隐含当前时间等。

2.2.3 字幕位置

通过设置字幕显示的行列位置,可以实现字符在屏幕的任何位置的显示。

2.2.4 时间设置

通过设置年、月、日、时、分

评论