采用FPGA提高广播应用的集成度

引言

在广播和传输系统中,采用一种或者两种串行接口来传输数字视频:没有压缩的数据使用视频串行数字接口(sdi)。压缩数据使用异步串行接口(asi),在视频设备中,主要采用移动图像和电视工程师联盟(smpte)定义的sdi来传送视频和音频数据。

视频设备能够支持标准清晰度(sd)、高清晰度(hd)数字视频格式,或者同时支持。sd视频传输的sdi速率为270mbps、360mbps或者540mbps,而hd视频传输的sdi速率为1.485 gbps或者1.485/1.001 gbps。hd提供高质量的视频,代表了今后数字视频广播的发展方向。随着hd视频需求的增长,要求硬件能够处理hd技术所需的大数据吞吐量。

在数字视频传送系统中,数据传送的主要方式是asi的270mbps单节目传送流(spts)或者多节目传送流(mpts),这些方式由数字视频广播(dvb)协会定义。

广播设备开发人员通常使用assp来实现sdi和dvb-asi功能,也可以利用可编程逻辑器件(pld),使用pld中的逻辑和其他嵌入式资源构建所需的各种数字功能,以实现这些接口。通过使用pld。可以显著降低总成本。某些情况下,在每asi通道或者每sdi端口的基础上,pld不到assp成本的1/10。

sdi的可编程逻辑解决方案

要达到sdi和dvb-asi需要的270mbps数据速率,可编程解决方案需要提供以下功能:

lvds i/o足够的逻辑容量

数据恢复能力

产生时钟信号的pll

对于hd-sdi数据速率,需要采用支持嵌入式serdes技术、时钟数据恢复,并集成了高速收发器通道的pld,例如altera的stratix gx系列fpga。

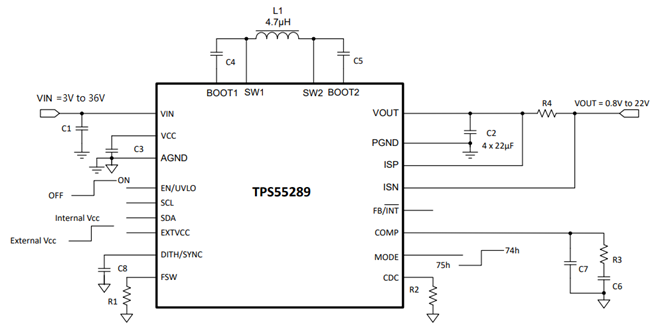

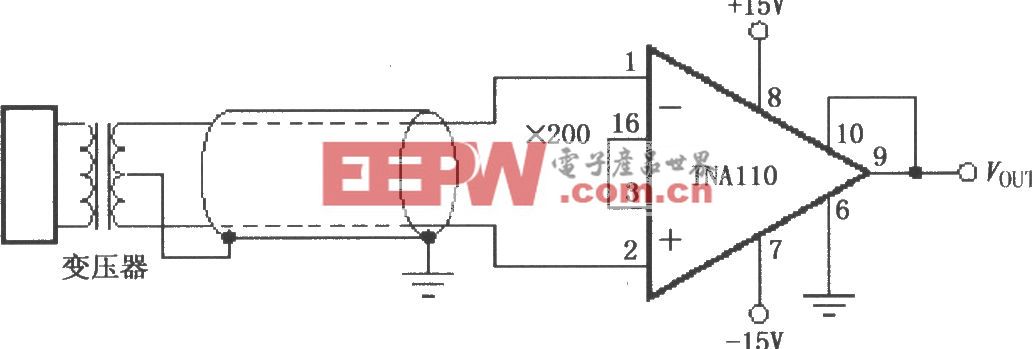

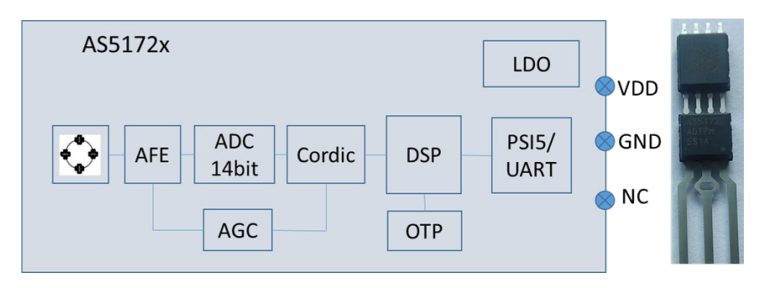

图1所示为altera可编程逻辑中实现sd-sdi和hd-sdi功能所需的构成单元。sd-sdi解决方案在逻辑单元(le)中利用过采样技术来恢复数据。fpga中的基本构建模块le在serdes模块中表示为“软逻辑”。在hd-sdi解决方案中,嵌入式serdes和cdr电路完成时钟和数据恢复功能。

hd-sdi方案中的其他功能包括发射机侧的线编号插入和循环冗余校验(crc)计算,以及接收机侧的线编号提取和循环冗余校验。

基于可编程逻辑的dvb-asi解决方案

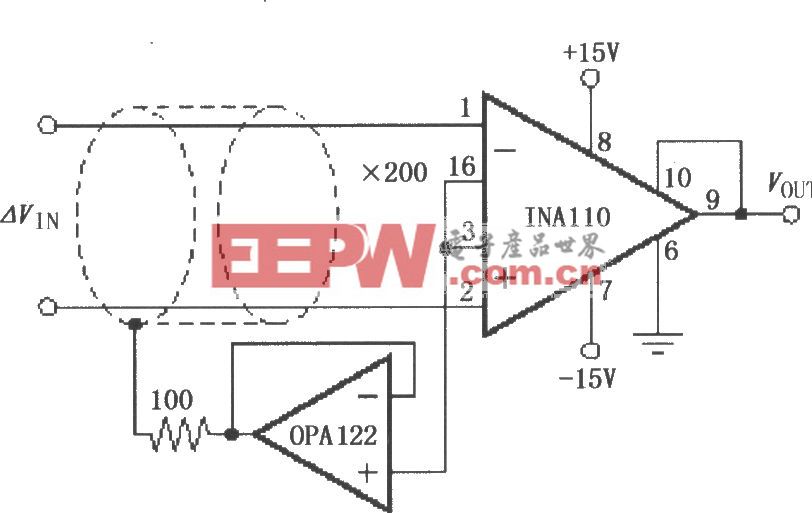

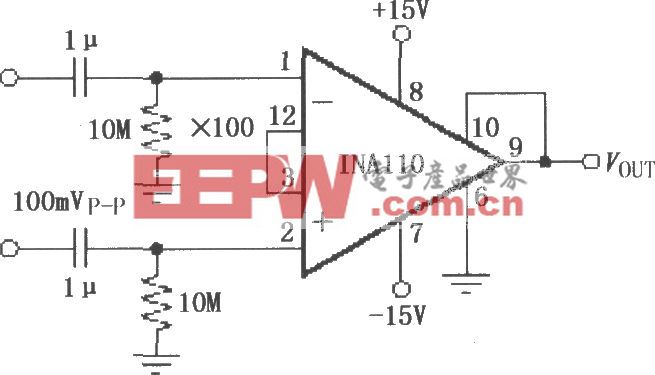

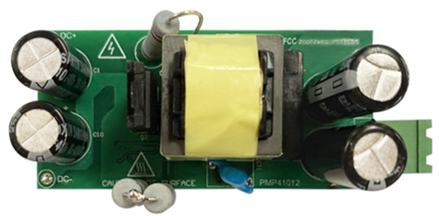

可以采用fpga来实现dvb-asi所需的数据速率,fpga为asi接收机和发射机输入基准时钟提供pll。altera的cyclone、stratix和stratix gx系列fpga具备这些功能。图2所示为在fpga中实现dvb-asi所需的构成单元,包括发射机和接收机耦合的回环通道,以及用于内置测试操作的伪随机二进制序列(prbs)校验器和prbs产生器。

asi接收机组成为:

解串器,将到达的串行数据转换为10比特宽的并行数据过采样接口,实现数据恢复和位同步

字对齐

8位/10位编码器,将10位并行数据转换为8位原始数据

同步状态机探测字同步或者同步丢失

速率匹配fifo缓冲匹配到达比特和发送(或者系统)时钟的速率。

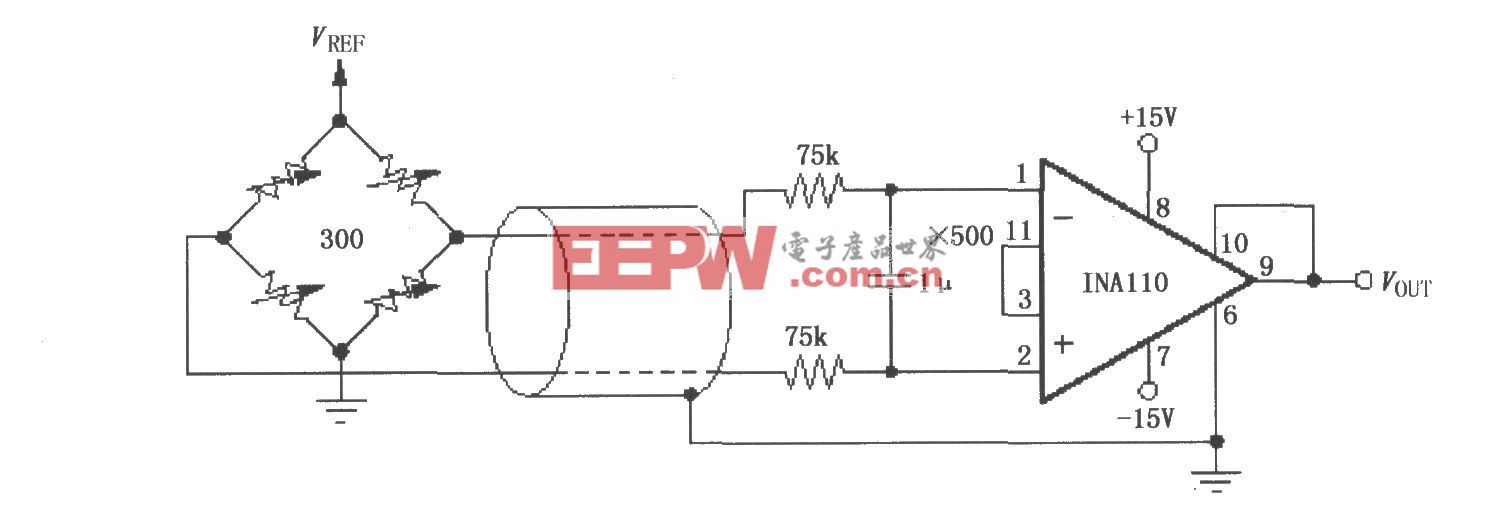

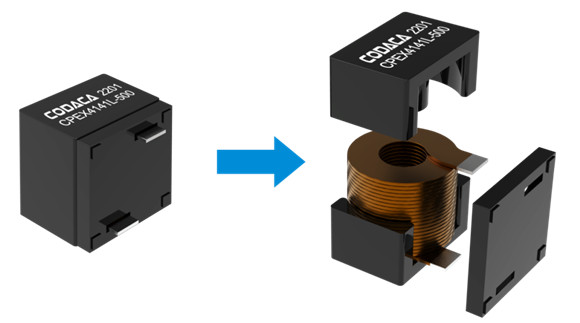

图3所示为asi接收机的构成单元,asi发射机含有一个8位/10位编码器和一个串化器,编码器将8位宽的字转换为10位,串化器将10位并行字转换为串行数据,采用一个10位移位寄存器实现该功能,以字速率从编码器输入,以lvds输出缓冲比特率输出。27m赫兹基准时钟乘以10的pll提供比特率时钟,支持抖动受控asi传输串化。asi发射机构成单元如图4所示。

在可编程逻辑中实现sdi和dvb-asi

一般情况下,采用fpga实现一个asi通道需要的le数量小于1000,cyclone ⅱ fpga每通道成本低于1美元,比现有assp方案低得多。

一个10位sd-sdi全双工端口在altera fpga中只需要400个le。对于cyclone ⅱ fpga中的10位sd-sdi数据,其每端口成本也远远低于现有的assp方案。对于20位hd-sdi数据,收发器通道逻辑大约需要1000个le,在stratix gx器件中实现这些逻辑时,每端口成本等于甚至低于assp的每端口成本。当考虑到可编程逻辑的其他集成性能时,stratix gx方案的优势更加突出。

可编程逻辑集成功能还具有其他优势

在典型应用中,dvb-asi和sdi只是广播设备全部功能的一部分,例如,dvb-asi通常用于广播数据转发系统,需要进行视频复用、压缩、调制和解调、时隙复用、编解码等信号处理,这些操作需要前向纠错(fec)、滤波、间插、正交振幅调制(qam)映射、viterbi和reed-solomon解码等数字信号处理功能。这些功能可以利用fpga中的资源来实现,包括le、cyclone ⅱ器件中的乘法器,以及stratix器件中的dsp模块。

通过将这些功能集成到几个器件中,基于fpga的解决方案进一步降低了开发成本,节省了电路板空间,降低了系统复杂性,fpga所具有的灵活性使开发人员能够定制实现设计中每一单元之间的接口,在最短的时间内加入各种功能,突出设计质量,设计人员还可以得到与单个可编程器件相同的asi通道或者sdi端口数,而采用assp就必须使用多个分立器件。

参考设计加速产品上市

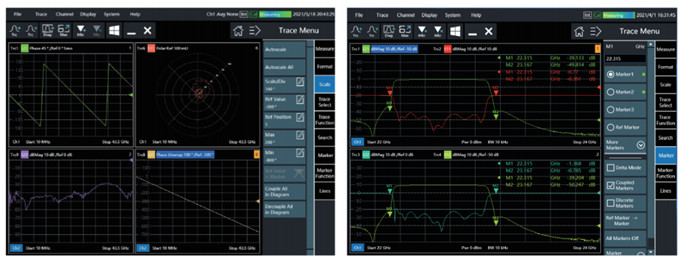

在sdi参考设计中,对三个smpte建议抖动参数进行了评估:

抖动产生器——器件或者系统产生一个串行数字信号(在这种情况下是hd-sdi),它含有某一振幅和频率的正弦抖动。产生的抖动也可以是非正弦的。接收抖动容限——当应用于器件或者系统输入时,正弦抖动的峰-峰值振幅会导致性能劣化。

抖动传送——输入抖动导致的器件或者系统输出抖动。

dvb-asi标准并没有针对抖动容限提供任何规范,但可以采用下面的抖动参数评估altera的dvb-asi参考设计:

发射机的抖动产生接收机的抖动容限

接收机灵敏度

输出振幅和边沿速率

cyclone视频演示板和stratix gx串行视频演示说明板可以演示这些参考设计。

结语

与assp相比,altera的dvb-asi和sdi可编程逻辑解决方案能够显著降低广播设备的开发成本,将dvb-asi和sdi功能集成到少量器件中,进一步降低了成本、节省了电路板空间、降低了复杂性。

评论