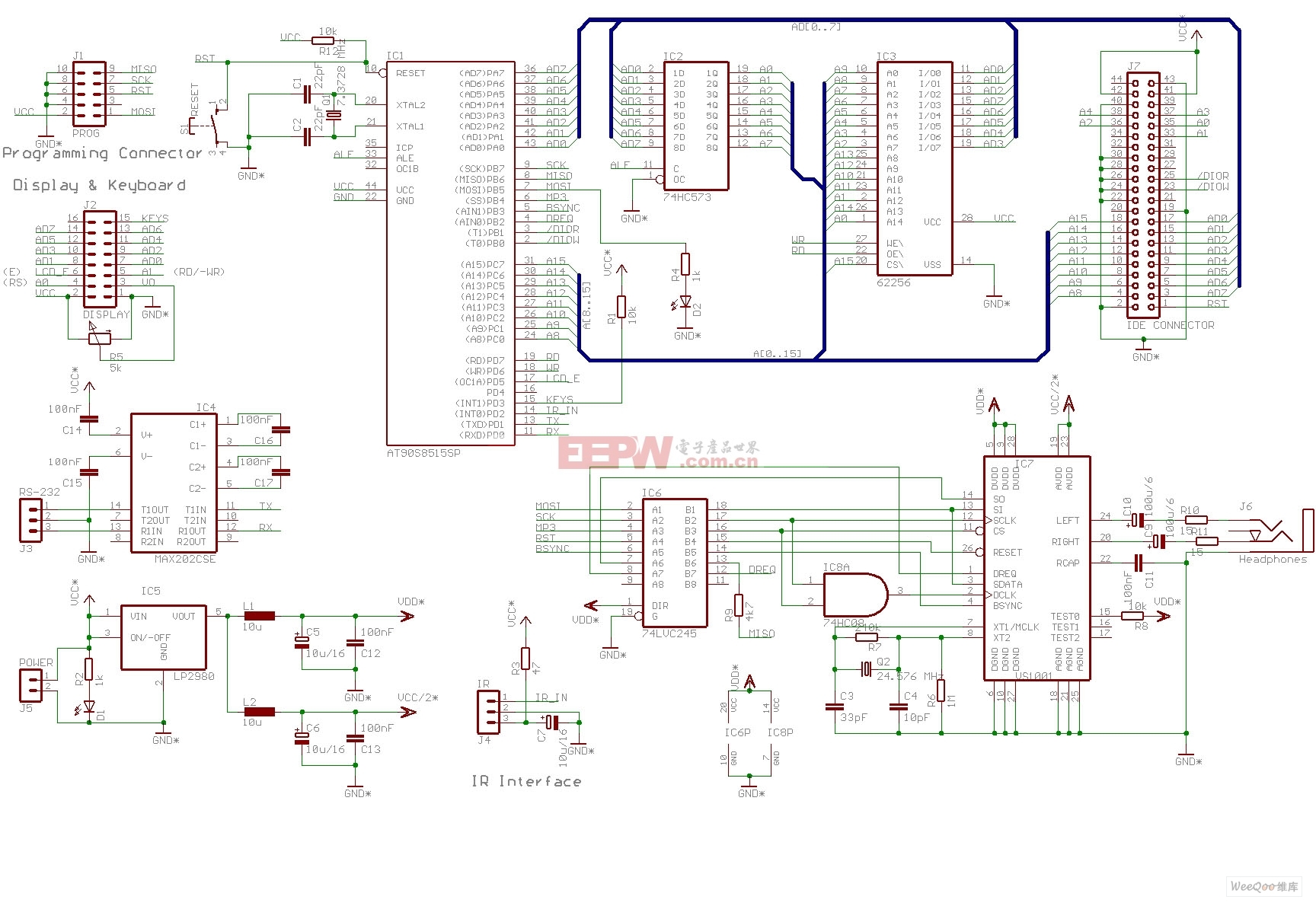

FPGA电路

在附图一的FPGA电路中,列举其中功能比较重要者说明如下:

●主电路:这是完整的数据路径----从微控制器总线到可共享的参数/地址映像内存、到DRAM/IDE总线。它包含了微控制器能够存取的所有外部缓存器、事件侦测(event detection)和移动请求位(action request bits)。外部缓存器组是位于DRAM内,执行各种特定的任务;当关机时,这些缓存器将会消失。事件侦测、移动请求位都是为了让微控制器得知目前的状态,并采取适当的移动、或执行特定的韧体程序。

●控制用的状态机:负责接收各种移动请求位,并使所有的控制线生效(assert),最后导致数据移动。它是一种简单的,但大型的状态机;平时它处于闲置和等待的状态,直到要采取移动。所有的状态是采用S_state_#的方式命名的。OR闸在适当的状态下,会使正确的控制讯号生效,如附图二所示。这个电路也包含了「优先级编码器(priority encoder)」。在闲置状态时,若搁置了许多个请求,则优先级编码器可以决定哪一个要先执行。这种电路虽然有点复杂,但是它使用「一热(one-hot)」的简单概念。所谓「一热」是指每一个状态是使用一个正反器(flip-flop)实现的,在每一个状态下,只有一个正反器是处于高值,其余都是低值,而且「热位(hot bit)」会一直移动,直到回到闲置状态。在DMA路径上,具有一个正反器(也可以省略不用),当结束DMA作业的条件成立时(ISZERO),此正反器会收到「热位」。所有的控制讯号是由OR闸产生的,只要输入的状态讯号群组中有一个是高值,OR闸就会输出高值(使控制讯号生效)。例如:若(图二)的OR2的S_RD_IDE_1或S_WR_IDE_1为高值,则IDE_ADDR的输出也会是高值,因此IDE_ADDR生效了。不过,有一些对时间要求很严格的(timing critical)讯号,并不是使用OR闸产生的,它们是使用建立/重置(set/reset)缓存器产生的。建立/重置缓存器的功效和OR闸一样,但是没有延迟。

微控制器总线MOVX侦测

倾听微控制器总线,当没有MOVX指令要执行时,使DMA_OK讯号生效。当DMA_OK未生效时,优先级编码器不会让任何非CPU的硬件单元存取DRAM。所以,它对微控制器的读取和写入请求是立即响应的,不会有延迟发生。这对8051微控制器而言,是很重要的,因为8051没有等待状态。如果有侦测到一个MOVX作业码,但是MOVX没有被执行,一个31周期的定时器可以使DMA_OK再次生效。

■微控制器的地址译码

这些讯号生效后,可以使外部缓存器在微控制器的内存映像区域内使用。通常,这是将地址排线和REG_RD讯号或REG_WR讯号AND在一起;REG_RD和REG_WR讯号是由状态机产生的。

■DRAM/IDE地址多任务器(mux)

在DRAM的行列式地址位(address bits)、IDE的地址位(来自于微控制器)之间,做DRAM/IDE地址脚位的切换;或为零,当执行IDE DMA的直接传输作业时(类似PIO)。

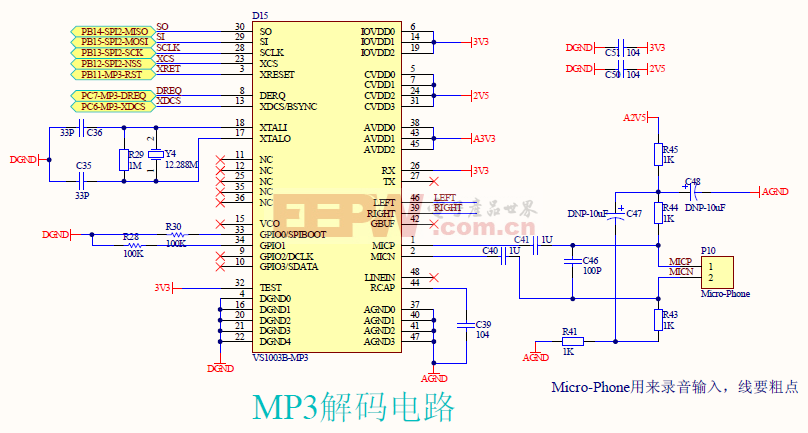

■MP3输出位移缓存器(shift register)

这是16位的位移缓存器,它从IDE接口得到一个16位的字组(word),并以位移的方式将此字组送至 MP3译码器。

■MP3位计数器

计算位移缓存器送至MP3译码器的位数目。当所有的16位都被移出时,会产生一个讯号,此时,位移缓存器准备供给STA013 DMA使用,以继续从DRAM中读取和传送下一个字组。

■DRAM的重清(refresh)时脉

这个电路会每15.2 ?s 产生一个脉冲,要求状态机执行一个DRAM重清周期。此脉冲会在主电路内,建立一个请求旗标,当总线可以使用时,状态机会开始执行重清作业,而且优先等级比较高的请求不会被搁置。

■DRAM/IDE地址缓冲器(buffer)

保存地址,这些地址是用来驱动DRAM和IDE接口。

■32-byte的SRAM内存

使用两个16×16宽度的DRAM内存,将它们虚拟成具有地址或数据锁定(latch)功能的SRAM。其中一个保存DRAM的分页(page)号码,这些分页是映像至微控制器的地址空间0xFF00至0xFF1F的区域(DRAM_PAGE_CFG缓存器),它们和微控制器的12个地址位一起被送至DRAM/IDE地址多任务器,最后可以为DRAM的读写作业,产生一个唯一的地址。第二个SRAM负责保存DMA的参数值(在0xFF20至0xFF3F的区域内)。微控制器的外部内存(DRAM)空间映像如附(表一)所示。

■地址映像内存的写入功能生效

允许对地址映像内存进行写入作业。不过,它只允许微控制器在0xFF00至0xFF1F的内存区域写入数据。

■DMA参数内存的写入功能生效

允许对DMA参数内存进行写入作业。微控制器能写入这些参数,而且,这些参数也可以被状态机更新,例如:在进行DMA传输作业时,状态机可以改变它们。

■16位的递增/递减电路

在进行DMA传输作业时,16位的递增/递减可以用来更新参数值。递增电路是为了计算DRAM的目标地址,递减电路是为了计算字组。DMA参数内存的输出值会被送至此电路中,而且也会被送至16个多任务器中,以允许DMA参数被转译成地址,就好像它们来自于微控制器的地址总线(address bus)一样。

■零、壹和奇数值检测器

当DMA参数值被改变时,这个电路能够立即得知;如果DMA参数值是零、壹或奇数地址,这个电路也能够通知状态机。当DMA参数值是零时,状态机会清除DMA的请求旗标,以终止DMA作业,并将「完成DMA传输」的中断旗标设为1。

■微控制器的「地址锁定致能(address latch enable;ALE)」讯号之同步

能使微控制器的ALE讯号和FPGA 的时脉同步。微控制器的其它控制讯号也是采用类似的同步机制,但是它们位于主电路中。

■2:1多任务器/4位

此电路允许在每32 byte内存内的地址,可以被内存的一般功能控制,或被微控制器的总线控制(当韧体从这些缓存器中读出或写入,来改变地址映像或建立DMA传输时)。

■2:1多任务器/8位

它被使用在IDE区块内。它允许从微控制器的数据区域中,将数据加载至输出缓冲器内。

■2:1多任务器/16位

当执行一个DMA周期时,利用这个电路,可以从微控制器的地址总线(一般作业),切换成DMA参数内存的地址总线。

■2:1多任务器/16位

利用这个电路可以选择DMA参数内存的输入值;它是在更新的DMA参数(在一个DMA周期内)和微控制器的数据总线(当微控制器写入DMA设定值)之间做切换。单独设计这个16位的多任务器,是因为FPGA开发工具的「可设定的逻辑区块(configurable logic block;CLB)」之映像,无法将额外的逻辑闸纳入上列的那些2:1多任务器内(如此会浪费8个CLB,并在重要的时序路径上,增加额外的延迟时间),除非逻辑闸是在同一个电路设计图内。

■16至8位总线,三态(tri-state)缓冲器

此三态缓冲器允许一个16位总线的任一半字节(8 bit)去驱动一个8位总线。它可以让微控制器从宽16位的内存中读取数据。

■8至16位总线缓冲器

连接两个8位的总线成为一个16位总线(但FPGA开发工具并不会因此混淆)。

■8至16位总线缓冲器

连接一个8位的总线两次,成为一个16位总线(但FPGA开发工具并不会因此混淆)。此16位总线的任一半字节都是来自于此8位总线,如附(图三)。

■8位缓存器

一个8位缓存器,用来收集微控制器的地址位。

此外,由于不同的FPGA开发工具的性能差异,可能还需要:

●数个具有不同位数(例如:5至9位)的位移缓存器:它们在状态机中使用。可以避免因为在同一电路设计图内具有太多的符号,而使FPGA开发工具当机。

●正反器(在CLB中):这是唯一的CLB正反器,以一个比在FPGA开发链接库(library)中还要小的符号来重设计。

●正反器(在IOB中):这是唯一的「I/O区块(IOB)」正反器,以一个比在FPGA开发链接库(library)中还要小的符号来重设计。

FPGA电路算是此MP3播放机系统中,比较复杂的一部份,一般的OEM/ODM可以指定规格委外设计。另一个OEM/ODM厂商必须注意的是韧体的设计;或许韧体也可以委外设计,但是他们必须懂得如何使用底层韧体(汇编语言)所提供的应用程序接口(API),来设计上层的使用者程序(C语言程序)。

|

评论