NAND Flash的驱动程序设计方案

NAND Flash的驱动程序设计方案

以三星公司K9F2808UOB为例,设计了NAND Flash与S3C2410的接口电路,介绍了NAND Flash在ARM嵌入式系统中的设计与实现方法,并在UBoot上进行了验证。所设计的驱动易于移植,可简化嵌入式系统开发。

关键词 ARM UBoot NAND Flash K9F2808UOB 驱动程序

引言

当前各类嵌入式系统开发设计中,存储模块设计是不可或缺的重要方面。NOR和 NAND是目前市场上两种主要的非易失闪存技术。NOR Flash存储器的容量较小、写入速度较慢,但因其随机读取速度快,因此在嵌入式系统中,常用于程序代码的存储。与NOR相比,NAND闪存的优点是容量大,但其速度较慢,因为它的I/O端口只有8或16个,要完成地址和数据的传输就必须让这些信号轮流传送。NAND型Flash具有极高的单元密度,容量可以比较大,价格相对便宜。

本文以三星公司的 K9F2808UOB芯片为例,介绍了NAND Flash的接口电路与驱动的设计方法。文中介绍了开发NAND Flash驱动基本原理,意在简化嵌入式系统开发过程。

1 NAND Flash工作原理

S3C2410板的NAND Flash支持由两部分组成:集成在S3C2410 CPU上的NAND Flash控制器

和NAND Flash存储芯片。要访问NAND Flash中的数据,必须通过NAND Flash控制器发送命令才能完成。所以, NAND Flash相当于S3C2410的一个外设,并不位于它的内存地址区。

1.1 芯片内部存储布局及存储操作特点

一片NAND Flash为一个设备, 其数据存储分层为:1设备=4 096块;1块=32页;1页=528字节=数据块大小(512字节)+OOB块大小(16字节)。在每一页中,最后16字节(又称OOB,Out?of?Band)用于NAND Flash命令执行完后设置状态用,剩余512字节又分为前半部分和后半部分。可以通过NAND Flash命令00h/01h/50h分别对前半部、后半部、OOB进行定位,通过NAND Flash内置的指针指向各自的首地址。

存储操作特点有: 擦除操作的最小单位是块;NAND Flash芯片每一位只能从1变为0,而不能从0变为1,所以在对其进行写入操作之前一定要将相应块擦除(擦除即是将相应块的位全部变为1);OOB部分的第6字节(即517字节)标志是否是坏块,值为FF时不是坏块,否则为坏块。除OOB第6字节外,通常至少把OOB的前3字节用来存放NAND Flash硬件ECC码。

1.2 NAND Flash接口电路

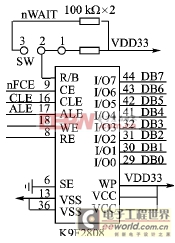

首先介绍开发板的硬件设计,图1为NAND Flash接口电路。其中开关SW的1、2连接时R/B表示准备好/忙,2、3连接时nWAIT可用于增加读/写访问的额外等待周期。在S3C2410处理器中已经集成了NAND Flash控制器,图2为微控制器与NAND Flash连接的方式。

图1 NAND Flash接口电路

1.3 控制器工作原理

NAND Flash控制器在其专用寄存器区(SFR)地址空间中映射有属于自己的特殊功能寄存器,就是通过将NAND Flash芯片的内设命令写到其特殊功能寄存器中,从而实现对NAND Flash芯片读、检验和编程控制。特殊功能寄存器有:NFCONF、NFCMD、NFADDR、NFDATA、NFSTAT、NFECC。

评论